# Chapter 1 Electrons and Holes in Semiconductors

## 1.1 Silicon Crystal Structure

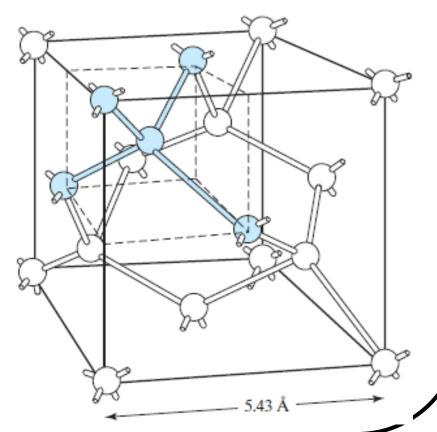

- *Unit cell* of silicon crystal is cubic.

- Each Si atom has 4 nearest neighbors.

## Silicon Wafers and Crystal Planes

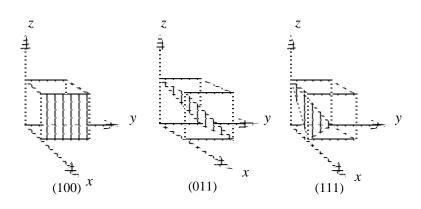

• The standard notation for crystal planes is based on the cubic unit cell.

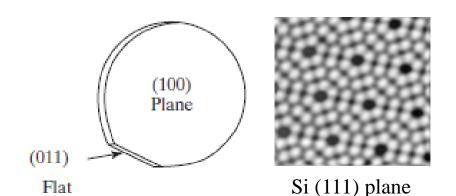

• Silicon wafers are usually cut along the (100) plane with a flat or notch to help orient the wafer during IC fabrication.

# 1.2 Bond Model of Electrons and Holes

; Si; Si; Si;

; Si ; Si ; Si ;

: Si : Si : Si :

Si Si Si Si

Si Si Si

Si Si Si Si

• Silicon crystal in a two-dimensional representation.

Si Si Si

• When an electron breaks loose and becomes a *conduction electron*, a *hole* is also created.

## Dopants in Silicon

- As, a Group V element, introduces conduction electrons and creates *N-type silicon*, and is called a *donor*.

- B, a Group III element, introduces holes and creates *P-type silicon*, and is called an *acceptor*.

- Donors and acceptors are known as dopants. Dopant ionization energy ~50meV (very low).

Hydrogen:

$$E_{ion} = \frac{m_0 q^4}{8\varepsilon_0^2 h^2} = 13.6 \text{ eV}$$

## GaAs, III-V Compound Semiconductors, and Their Dopants

Ga: As : Ga:

As: Ga: As:

Ga: As: Ga:

Ga: As:

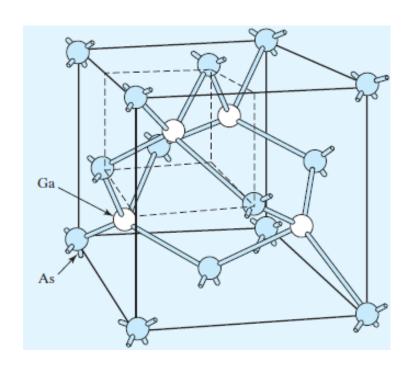

- GaAs has the same crystal structure as Si.

- GaAs, GaP, GaN are III-V compound semiconductors, important for optoelectronics.

- Wich group of elements are candidates for donors? acceptors?

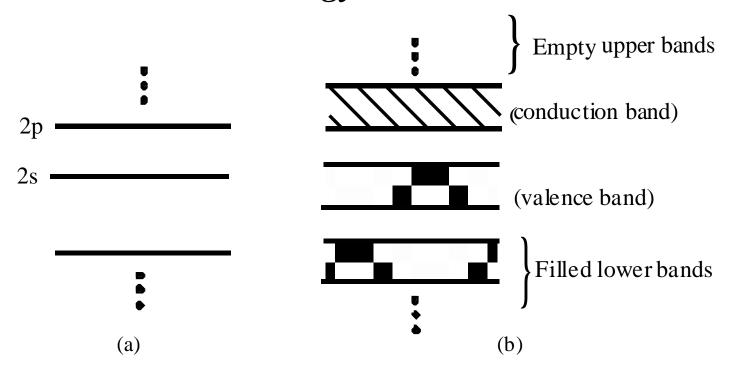

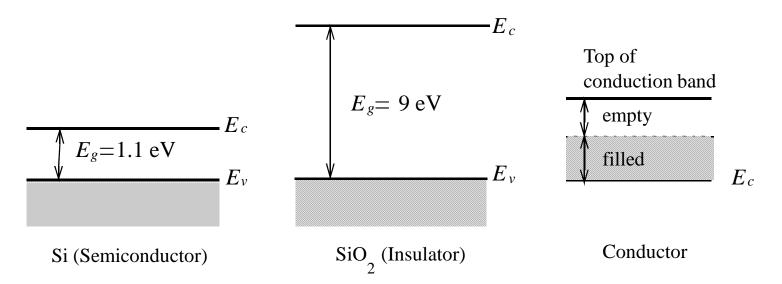

## 1.3 Energy Band Model

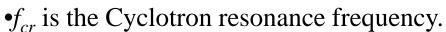

- Energy states of Si atom (a) expand into energy bands of Si crystal (b).

- The lower bands are filled and higher bands are empty in a semiconductor.

- The highest filled band is the *valence band*.

- The lowest empty band is the *conduction band*.

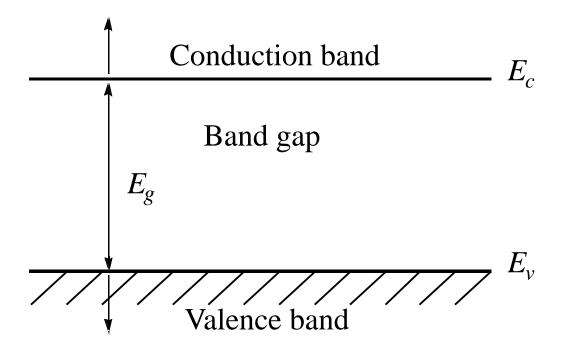

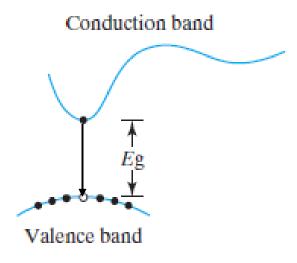

## 1.3.1 Energy Band Diagram

- *Energy band diagram* shows the bottom edge of conduction band,  $E_c$ , and top edge of valence band,  $E_v$ .

- $E_c$  and  $E_v$  are separated by the **band gap energy**,  $E_g$ .

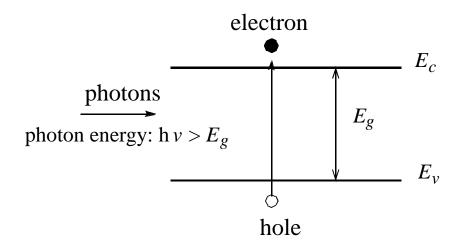

## Measuring the Band Gap Energy by Light Absorption

•  $E_g$  can be determined from the minimum energy (h v) of photons that are absorbed by the semiconductor.

#### Bandgap energies of selected semiconductors

| Semi-<br>conductor | InSb | Ge   | Si   | GaAs | GaP  | ZnSe | Diamond |

|--------------------|------|------|------|------|------|------|---------|

| Eg (eV)            | 0.18 | 0.67 | 1.12 | 1.42 | 2.25 | 2.7  | 6       |

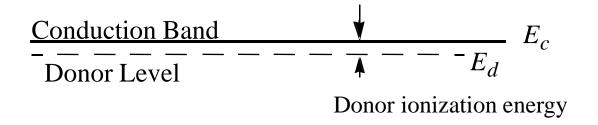

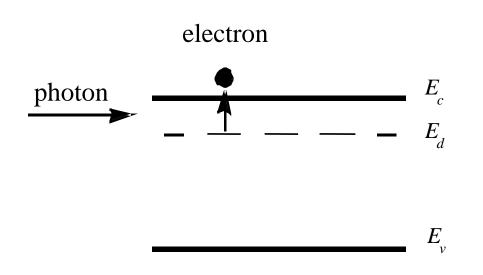

## 1.3.2 Donor and Acceptor in the Band Model

#### Ionization energy of selected donors and acceptors in silicon

|                                                     | Donors |    | Acceptors |    |    |     |

|-----------------------------------------------------|--------|----|-----------|----|----|-----|

| Dopant                                              | Sb     | P  | As        | В  | Al | In  |

| Ionization energy, $E_c - E_d$ or $E_a - E_v$ (meV) | 39     | 44 | 54        | 45 | 57 | 160 |

## 1.4 Semiconductors, Insulators, and Conductors

- Totally filled bands and totally empty bands do not allow current flow. (Just as there is no motion of liquid in a totally filled or totally empty bottle.)

- Metal conduction band is half-filled.

- Semiconductors have lower  $E_g$ 's than insulators and can be doped.

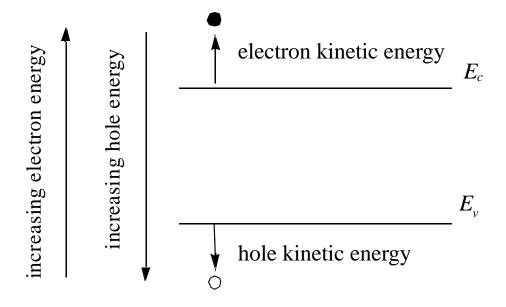

#### 1.5 Electrons and Holes

- Both electrons and holes tend to seek their lowest energy positions.

- Electrons tend to fall in the energy band diagram.

- Holes float up like bubbles in water.

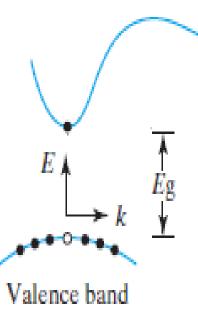

#### 1.5.1 Effective Mass

The electron wave function is the solution of the three dimensional Schrodinger wave equation

$$-\frac{\hbar^2}{2m_0}\nabla^2\psi + V(r)\psi = \psi$$

The solution is of the form  $\exp(\pm \mathbf{k} \cdot \mathbf{r})$   $k = \text{wave vector} = 2\pi/\text{electron wavelength}$ For each k, there is a corresponding E.

acceleration =

$$-\frac{q\varepsilon}{\hbar^2} \frac{d^2 E}{dk^2} = \frac{F}{m}$$

effective mass

$$\equiv \frac{\hbar^2}{d^2 E / dk^2}$$

Conduction band

#### 1.5.1 Effective Mass

In an electric field, **E**, an electron or a hole accelerates.

$$a = \frac{-q \, \mathcal{E}}{m_n} \qquad \text{electrons}$$

$$a = \frac{q\mathcal{E}}{m_p} \qquad \text{holes}$$

#### **Electron and hole effective masses**

|           | Si   | Ge   | GaAs  | InAs  | AlAs |

|-----------|------|------|-------|-------|------|

| $m_n/m_0$ | 0.26 | 0.12 | 0.068 | 0.023 | 2    |

| $m_p/m_0$ | 0.39 | 0.3  | 0.5   | 0.3   | 0.3  |

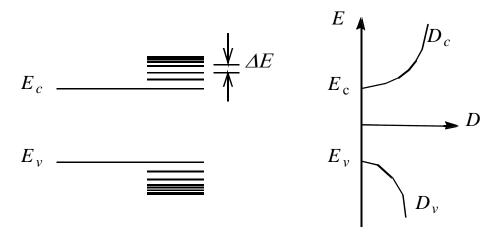

#### 1.5.2 How to Measure the Effective Mass

Cyclotron Resonance Technique

Centripetal force = Lorentzian force

$$\frac{m_n v^2}{r} = q v B$$

$$v = \frac{qBr}{m_n}$$

- •It is independent of v and r.

- •Electrons strongly absorb microwaves of that frequency.

- •By measuring  $f_{cr}$ ,  $m_n$  can be found.

Microwave

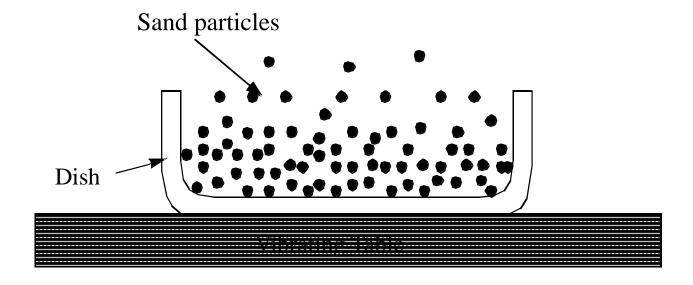

# 1.6 Density of States

$$D_c(E) = \frac{\text{number of states in } \Delta E}{\Delta E \cdot \text{volume}} \left( \frac{1}{\text{eV} \cdot \text{cm}^3} \right)$$

$$D_c(E) \equiv \frac{8\pi m_n \sqrt{2m_n(E - E_c)}}{h^3}$$

$$D_{\nu}(E) \equiv \frac{8\pi m_p \sqrt{2m_p (E_{\nu} - E)}}{h^3}$$

Derived in Appendix I

# 1.7 Thermal Equilibrium and the Fermi Function 1.7.1 An Analogy for Thermal Equilibrium

• There is a certain probability for the electrons in the conduction band to occupy high-energy states under the agitation of thermal energy.

# Appendix II. Probability of a State at E being Occupied

- •There are  $g_1$  states at  $E_1$ ,  $g_2$  states at  $E_2$ ... There are N electrons, which constantly shift among all the states but the average electron energy is fixed at 3kT/2.

- •There are many ways to distribute N among  $n_1$ ,  $n_2$ ,  $n_3$ ....and satisfy the 3kT/2 condition.

•The equilibrium distribution is the distribution that maximizes the number of combinations of placing  $n_1$  in  $g_1$  slots,  $n_2$  in  $g_2$  slots....:  $n_1/g_1 = \frac{1}{1 + e^{(E - E_F)/kT}}$

$E_F$  is a constant determined by the condition  $\sum n_i = N$

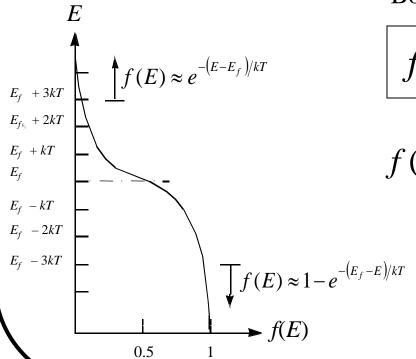

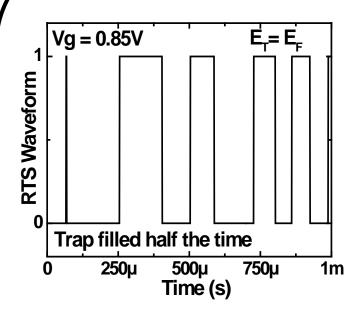

## 1.7.2 Fermi Function—The Probability of an Energy State Being Occupied by an Electron

$$f(E) = \frac{1}{1 + e^{(E - E_f)/kT}}$$

$E_f$  is called the  $F$  the  $F$  the  $F$  the  $F$  and  $F$  is called the  $F$  the  $F$  and  $F$  are  $F$  and  $F$  are  $F$  and  $F$  are  $F$  and  $F$  are  $F$  are  $F$  are  $F$  and  $F$  are  $F$  are  $F$  are  $F$  and  $F$  are  $F$  are  $F$  and  $F$  are  $F$  are  $F$  and  $F$  are  $F$  are  $F$  are  $F$  are  $F$  are  $F$  and  $F$  are  $F$  are  $F$  and  $F$  are  $F$  are  $F$  and  $F$  are  $F$  are  $F$  are  $F$  are  $F$  are  $F$  and  $F$  are  $F$  are  $F$  and  $F$  are  $F$  are  $F$  are  $F$  are  $F$  and  $F$  are  $F$  and  $F$  are  $F$  are  $F$  are  $F$  and  $F$  are  $F$  are  $F$  are  $F$  and  $F$  are  $F$  are  $F$  and  $F$  are  $F$  and  $F$  are  $F$  are  $F$  are  $F$  are  $F$  are  $F$  and  $F$  are  $F$  are  $F$  and  $F$  are  $F$  are  $F$  and  $F$  are  $F$  are  $F$  are  $F$  are  $F$  are  $F$  and  $F$  are  $F$  are  $F$  are  $F$  and  $F$  are  $F$  and  $F$  are  $F$  and  $F$  are  $F$  and  $F$  are  $F$  are

$E_f$  is called the *Fermi energy* or the *Fermi level*.

Boltzmann approximation:

$$f(E) \approx e^{-(E-E_f)/kT}$$

$E-E_f >> kT$

$$f(E) \approx 1 - e^{-(E_f - E)/kT}$$

$E - E_f \ll -kT$

Remember: there is only one Fermi-level in a system at equilibrium.

### 1.8 Electron and Hole Concentrations

## 1.8.1 Derivation of n and p from D(E) and f(E)

$$n = \int_{E_c}^{\text{top of conduction band}} f(E)D_c(E)dE$$

$$n = \frac{8\pi m_n \sqrt{2m_n}}{h^3} \int_{E_c}^{\infty} \sqrt{E - E_c} e^{-(E - E_f)/kT} dE$$

$$= \frac{8\pi m_n \sqrt{2m_n}}{h^3} e^{-(E_c - E_f)/kT} \int_0^{E - E_c} \sqrt{E - E_c} e^{-(E - E_c)/kT} d(E - E_c)$$

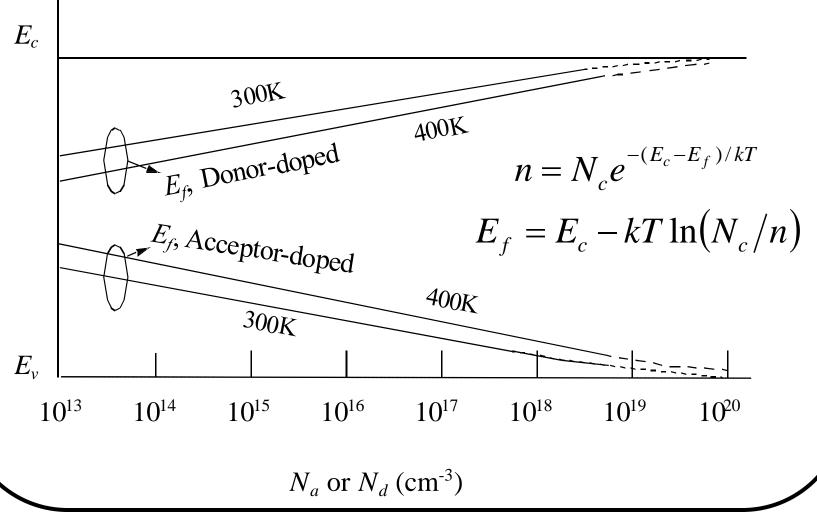

### Electron and Hole Concentrations

$$n = N_c e^{-(E_c - E_f)/kT}$$

$$N_c \equiv 2 \left[ \frac{2\pi m_n kT}{h^2} \right]^{3/2}$$

$$p = N_{v}e^{-(E_{f}-E_{v})/kT}$$

$$N_{v} \equiv 2 \left[ \frac{2\pi m_{p} kT}{h^{2}} \right]^{3/2}$$

$N_c$  is called the *effective* density of states (of the conduction band).

$N_v$  is called the *effective* density of states of the valence band.

Remember: the closer  $E_f$  moves up to  $N_c$ , the larger n is; the closer  $E_f$  moves down to  $E_v$ , the larger p is.

For Si,  $N_c = 2.8 \cdot 10^{19} \text{cm}^{-3}$  and  $N_v = 1.04 \cdot 10^{19} \text{cm}^{-3}$ .

#### 1.8.2 The Fermi Level and Carrier Concentrations

Where is  $E_f$  for  $n = 10^{17}$  cm<sup>-3</sup>? And for  $p = 10^{14}$  cm<sup>-3</sup>?

**Solution**: (a)

$$n = N_c e^{-(E_c - E_f)/kT}$$

$$E_c - E_f = kT \ln(N_c/n) = 0.026 \ln(2.8 \times 10^{19} / 10^{17}) = 0.146 \text{ eV}$$

(b) For

$$p = 10^{14} \text{cm}^{-3}$$

, from Eq.(1.8.8),

$$E_f - E_v = kT \ln(N_v/p) = 0.026 \ln(1.04 \times 10^{19} / 10^{14}) = 0.31 \text{ eV}$$

$$E_{v} \qquad \begin{array}{c} - \cdot \cdot \cdot \cdot \cdot - \cdot - \cdot - \cdot - E_{f} \\ \hline 0.31 \text{ eV} \\ \hline E_{v} \end{array}$$

### 1.8.3 The np Product and the Intrinsic Carrier Concentration

Multiply

$$n = N_c e^{-(E_c - E_f)/kT}$$

and  $p = N_v e^{-(E_f - E_v)/kT}$

$$np = N_c N_v e^{-(E_c - E_v)/kT} = N_c N_v e^{-E_g/kT}$$

$$np = n_i^2$$

$$n_i = \sqrt{N_c N_v} e^{-E_g/2kT}$$

- In an intrinsic (undoped) semiconductor,  $n = p = n_i$ .

- $n_i$  is the *intrinsic carrier concentration*, ~10<sup>10</sup> cm<sup>-3</sup> for Si.

#### **EXAMPLE:** Carrier Concentrations

**Question:** What is the hole concentration in an N-type semiconductor with  $10^{15}$  cm<sup>-3</sup> of donors?

**Solution:**  $n = 10^{15} \text{ cm}^{-3}$ .

$$p = \frac{n_i^2}{n} \approx \frac{10^{20} \text{ cm}^{-3}}{10^{15} \text{ cm}^{-3}} = 10^5 \text{ cm}^{-3}$$

After increasing T by 60 °C, n remains the same at  $10^{15}$  cm<sup>-3</sup> while p increases by about a factor of 2300 because  $n_i^2 \propto e^{-E_g/kT}$ .

**Question:** What is n if  $p = 10^{17} \text{cm}^{-3}$  in a P-type silicon wafer?

Solution:

$$n = \frac{n_i^2}{n} \approx \frac{10^{20} \text{ cm}^{-3}}{10^{17} \text{ cm}^{-3}} = 10^3 \text{ cm}^{-3}$$

## 1.9 General Theory of n and p

### EXAMPLE: Complete ionization of the dopant atoms

$N_d = 10^{17}$  cm<sup>-3</sup>. What fraction of the donors are not ionized?

Solution: First assume that all the donors are ionized.

$$n = N_d = 10^{17} \text{ cm}^{-3} \Rightarrow E_f = E_c - 146 \text{meV}$$

Probability of not being ionized

$$\approx \frac{1}{1 + \frac{1}{2}e^{(E_d - E_f)/kT}} = \frac{1}{1 + \frac{1}{2}e^{((146 - 45)\text{meV})/26\text{meV}}} = 0.04$$

Therefore, it is reasonable to assume complete ionization, i.e.,  $n = N_d$ .

## 1.9 General Theory of n and p

Charge neutrality:

$$n + N_a = p + N_d$$

$$np = n_i^2$$

$$p = \frac{N_a - N_d}{2} + \left[ \left( \frac{N_a - N_d}{2} \right)^2 + n_i^2 \right]^{1/2}$$

$$n = \frac{N_d - N_a}{2} + \left[ \left( \frac{N_d - N_a}{2} \right)^2 + n_i^2 \right]^{1/2}$$

# 1.9 General Theory of on n and p

I.

$$N_d - N_a >> n_i$$

(i.e., N-type)  $n = N_d - N_a$   $p = n_i^2/n$

$$n = N_d - N_a$$

$$p = n_i^2 / n$$

If

$$N_d \gg N_a$$

,  $n = N_d$  and  $p = n_i^2 / N_d$

**II.**

$$N_a - N_d >> n_i$$

(i.e., P-type)

II.

$$N_a - N_d >> n_i$$

(i.e., P-type)  $p = N_a - N_d$   $n = n_i^2/p$

If

$$N_a \gg N_d$$

,  $p = N_a$  and  $n = n_i^2 / N_a$

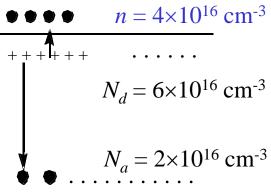

### EXAMPLE: Dopant Compensation

What are n and p in Si with (a)  $N_d = 6 \times 10^{16} \text{ cm}^{-3}$  and  $N_a = 2 \times 10^{16} \text{ cm}^{-3}$  and (b) additional  $6 \times 10^{16} \text{ cm}^{-3}$  of  $N_a$ ?

(a)

$$n = N_d - N_a = 4 \times 10^{16} \text{ cm}^{-3}$$

$p = n_i^2 / n = 10^{20} / 4 \times 10^{16} = 2.5 \times 10^3 \text{ cm}^{-3}$

(b)

$$N_a = 2 \times 10^{16} + 6 \times 10^{16} = 8 \times 10^{16} \text{ cm}^{-3} > N_d$$

$p = N_a - N_d = 8 \times 10^{16} - 6 \times 10^{16} = 2 \times 10^{16} \text{ cm}^{-3}$

$$n = n_i^2 / p = 10^{20} / 2 \times 10^{16} = 5 \times 10^3 \text{ cm}^{-3}$$

$$N_d = 6 \times 10^{16} \text{ cm}^{-3}$$

$$N_a = 8 \times 10^{16} \text{ cm}^{-3}$$

$$p = 2 \times 10^{16} \text{ cm}^{-3}$$

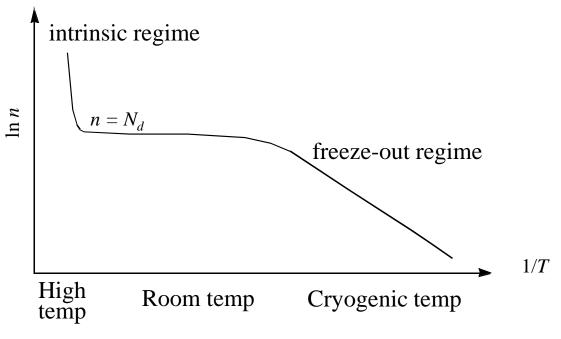

# 1.10 Carrier Concentrations at Extremely High and Low Temperatures

high T:

$$n = p = n_i = \sqrt{N_c N_v} e^{-E_g/2kT}$$

low T:

$$n = \left[ \frac{N_c N_d}{2} \right]^{1/2} e^{-(E_c - E_d)/2kT}$$

## Infrared Detector Based on Freeze-out

- •To image the black-body radiation emitted by tumors requires a photodetector that responds to  $h\vec{v}$ s around 0.1 eV.

- •In doped Si operating in the freeze-out mode, conduction electrons are created when the infrared photons provide the energy to ionized the donor atoms.

## 1.11 Chapter Summary

Energy band diagram. Acceptor. Donor.  $m_n$ ,  $m_p$ . Fermi function.  $E_f$ .

$$n = N_c e^{-(E_c - E_f)/kT}$$

$$p = N_v e^{-(E_f - E_v)/kT}$$

$$n = N_d - N_a$$

$$p = N_a - N_d$$

$$np = n_i^2$$

# Chapter 2 Motion and Recombination of Electrons and Holes

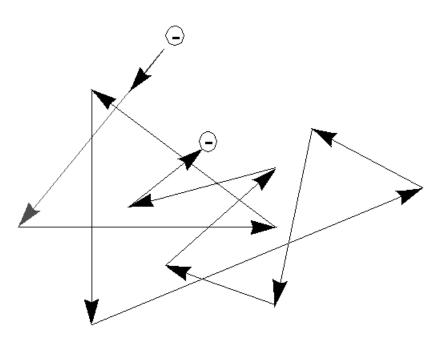

#### 2.1 Thermal Motion

Average electron or hole kinetic energy  $=\frac{3}{2}kT = \frac{1}{2}mv_{th}^2$

$$v_{th} = \sqrt{\frac{3kT}{m_{eff}}} = \sqrt{\frac{3 \times 1.38 \times 10^{-23} \text{JK}^{-1} \times 300 \text{K}}{0.26 \times 9.1 \times 10^{-31} \text{kg}}}$$

$$= 2.3 \times 10^5 \,\mathrm{m/s} = 2.3 \times 10^7 \,\mathrm{cm/s}$$

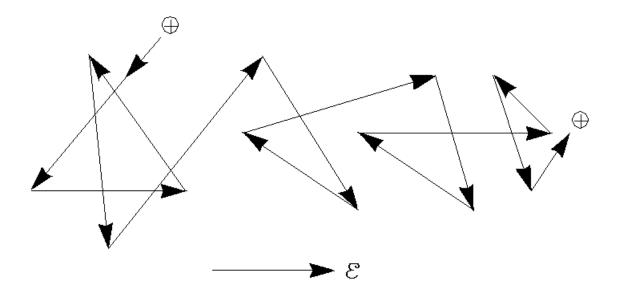

## 2.1 Thermal Motion

- Zig-zag motion is due to collisions or scattering with imperfections in the crystal.

- Net thermal velocity is zero.

- Mean time between collisions is  $\tau_m \sim 0.1 \text{ps}$

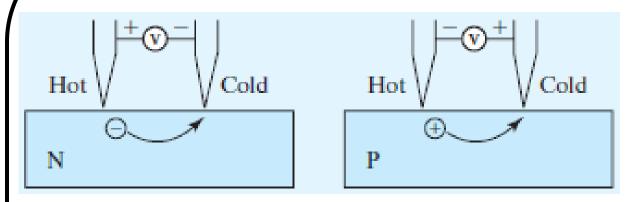

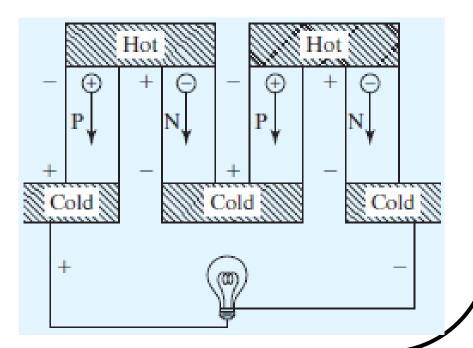

## Hot-point Probe can determine sample doing type

Hot-point Probe distinguishes N and P type semiconductors.

Thermoelectric Generator (from heat to electricity) and Cooler (from electricity to refrigeration)

# 2.2 *Drift*

#### 2.2.1 Electron and Hole Mobilities

• *Drift* is the motion caused by an electric field.

#### 2.2.1 Electron and Hole Mobilities

$$m_{_p}v=q\,\mathbf{E}\, au_{_{mp}}$$

$$_{\mathcal{V}}=rac{q\,\mathbf{E}\, au_{_{mp}}}{m_{_{p}}}$$

$$v=\mu_{p}\mathbf{E}$$

$$\mu_{p}=rac{q\, au_{mp}}{m_{p}}$$

$$u_p = \frac{1 - m_p}{m_p}$$

$$v = -\mu_n \mathbf{E}$$

$$\mu_n = \frac{q \, \tau_{mn}}{m_n}$$

•  $\mu_p$  is the hole mobility and  $\mu_n$  is the electron mobility

#### 2.2.1 Electron and Hole Mobilities

$$v = \mu \mathbf{E}$$

;  $\mu$  has the dimensions of  $v/\mathbf{E}$   $\left[\frac{\text{cm/s}}{\text{V/cm}} = \frac{\text{cm}^2}{\text{V} \cdot \text{s}}\right]$ .

## Electron and hole mobilities of selected semiconductors

|                                             | Si   | Ge   | GaAs | InAs  |

|---------------------------------------------|------|------|------|-------|

| $\mu_n (\text{cm}^2/\text{V}\cdot\text{s})$ | 1400 | 3900 | 8500 | 30000 |

| $\mu_p (\text{cm}^2/\text{V·s})$            | 470  | 1900 | 400  | 500   |

Based on the above table alone, which semiconductor and which carriers (electrons or holes) are attractive for applications in high-speed devices?

#### Drift Velocity, Mean Free Time, Mean Free Path

**EXAMPLE:** Given  $\mu_p = 470 \text{ cm}^2/\text{V} \cdot \text{s}$ , what is the hole drift velocity at  $\mathbf{E} = 10^3 \text{ V/cm}$ ? What is  $\tau_{mp}$  and what is the distance traveled between collisions (called the **mean free path**)? Hint: When in doubt, use the MKS system of units.

Solution:

$$v = \mu_p \mathbf{E} = 470 \text{ cm}^2/\text{V} \cdot \text{s} \times 10^3 \text{ V/cm} = 4.7 \times 10^5 \text{ cm/s}$$

$$\tau_{mp} = \mu_p m_p / q = 470 \text{ cm}^2/\text{V} \cdot \text{s} \times 0.39 \times 9.1 \times 10^{-31} \text{ kg/1.6} \times 10^{-19} \text{ C}$$

$$= 0.047 \text{ m}^2/\text{V} \cdot \text{s} \times 2.2 \times 10^{-12} \text{ kg/C} = 1 \times 10^{-13} \text{s} = 0.1 \text{ ps}$$

$$mean free path = \tau_{mh} v_{th} \sim 1 \times 10^{-13} \text{ s} \times 2.2 \times 10^7 \text{ cm/s}$$

$$= 2.2 \times 10^{-6} \text{ cm} = 220 \text{ Å} = 22 \text{ nm}$$

This is smaller than the typical dimensions of devices, but getting close.

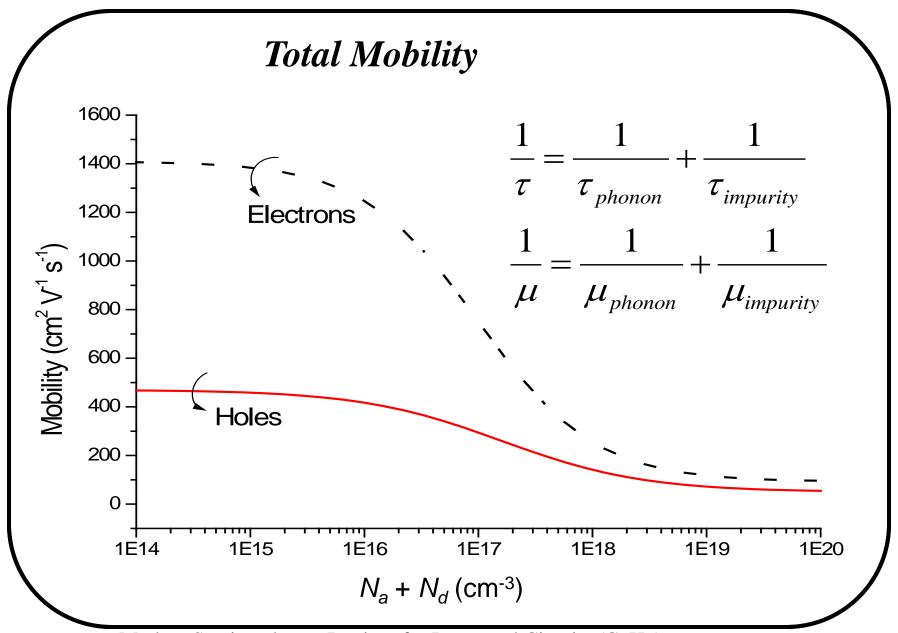

### 2.2.2 Mechanisms of Carrier Scattering

There are two main causes of carrier scattering:

- 1. Phonon Scattering

- 2. Ionized-Impurity (Coulombic) Scattering

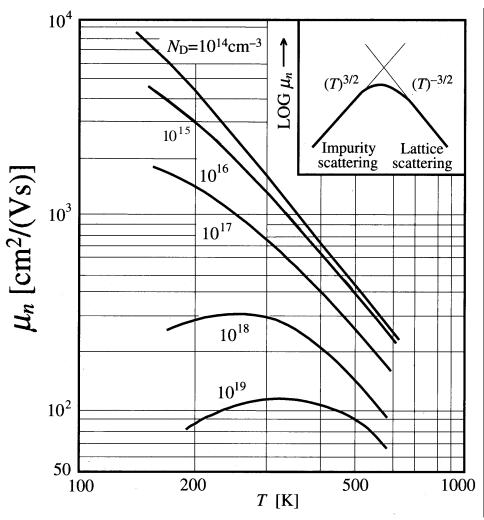

**Phonon scattering** mobility decreases when temperature rises:

$$\mu_{phonon} \propto \tau_{phonon} \propto \frac{1}{phonon \ density \times carrier \ thermal \ velocity} \propto \frac{1}{T \times T^{1/2}} \propto T^{-3/2}$$

$$\mu = q \tau / m \qquad \propto T$$

$$v_{th} \propto T^{1/2}$$

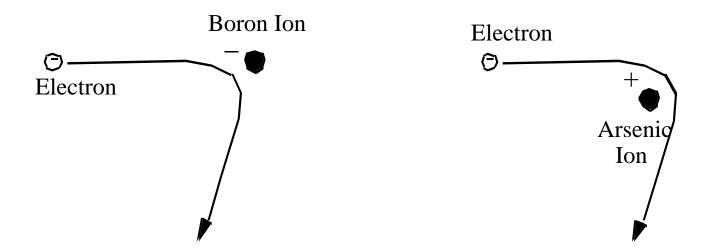

#### Impurity (Dopant)-Ion Scattering or Coulombic Scattering

There is less change in the direction of travel if the electron zips by the ion at a higher speed.

$$\mu_{impurity} \propto rac{v_{th}^3}{N_a + N_d} \propto rac{T^{3/2}}{N_a + N_d}$$

Question:

What  $N_d$  will make  $d\mu_n/dT = 0$  at room temperature?

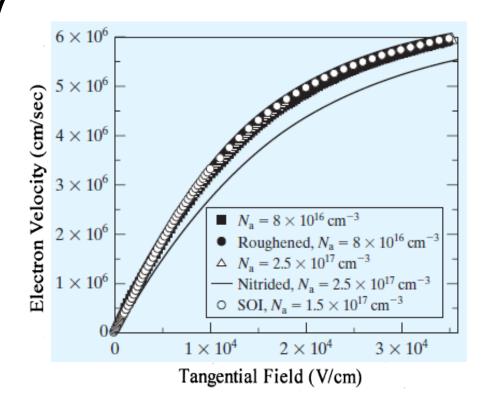

## Velocity Saturation

- When the kinetic energy of a carrier exceeds a critical value, it generates an optical phonon and loses the kinetic energy.

- Therefore, the kinetic energy is capped at large  $\mathbf{E}$ , and the velocity does not rise above a saturation velocity,  $v_{sat}$ .

- *Velocity saturation* has a deleterious effect on device speed as shown in Ch. 6.

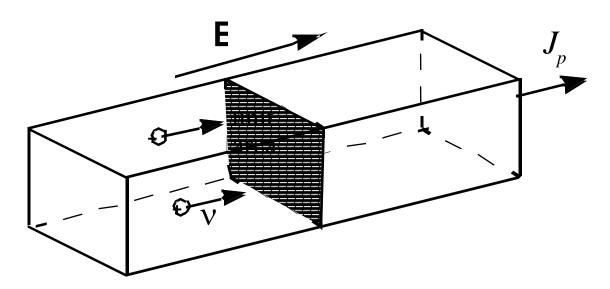

### 2.2.3 Drift Current and Conductivity

Hole current density

$$J_p = qpv$$

A/cm<sup>2</sup> or C/cm<sup>2</sup>·sec

EXAMPLE: If

$$p = 10^{15} \text{cm}^{-3}$$

and  $v = 10^{4} \text{ cm/s}$ , then  $J_{p} = 1.6 \times 10^{-19} \text{C} \times 10^{15} \text{cm}^{-3} \times 10^{4} \text{cm/s}$

=  $1.6 \text{ C/s} \cdot \text{cm}^{2} = 1.6 \text{ A/cm}^{2}$

## 2.2.3 Drift Current and Conductivity

$$J_{p,drift} = qpv = qp\mu_p$$

E

$$J_{n,drift} = -qnv = qn\mu_n$$

E

$$J_{drift} = J_{n,drift} + J_{p,drift} = \sigma \mathbf{E} = (qn\mu_n + qp\mu_p)\mathbf{E}$$

$\sigma = qn\mu_n + qp\mu_p$   $\sigma = qn\mu_n + qp\mu_p$

$1/\sigma$  = is resistivity (ohm-cm)

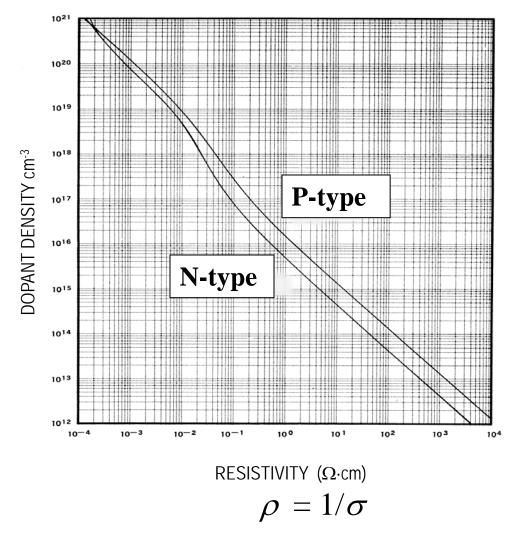

## Relationship between Resistivity and Dopant Density

## EXAMPLE: Temperature Dependence of Resistance

- (a) What is the resistivity ( $\rho$ ) of silicon doped with  $10^{17}$ cm<sup>-3</sup> of arsenic?

- (b) What is the resistance (R) of a piece of this silicon material  $1 \mu m$  long and  $0.1 \mu m^2$  in cross-sectional area?

#### Solution:

(a) Using the N-type curve in the previous figure, we find that  $\rho = 0.084 \ \Omega$ -cm.

(b)

$$R = \rho L/A = 0.084 \Omega \cdot \text{cm} \times 1 \mu \text{m} / 0.1 \mu \text{m}^2$$

=  $0.084 \Omega \cdot \text{cm} \times 10^{-4} \text{ cm} / 10^{-10} \text{ cm}^2$

=  $8.4 \times 10^{-4} \Omega$

## EXAMPLE: Temperature Dependence of Resistance

By what factor will R increase or decrease from T=300~K to T=400~K?

**Solution:** The temperature dependent factor in  $\sigma$  (and therefore  $\rho$ ) is  $\mu_n$ . From the mobility vs. temperature curve for  $10^{17} \text{cm}^{-3}$ , we find that  $\mu_n$  decreases from 770 at 300K to 400 at 400K. As a result, R increases by

$$\frac{770}{400} = 1.93$$

## 2.3 Diffusion Current

Particles diffuse from a higher-concentration location to a lower-concentration location.

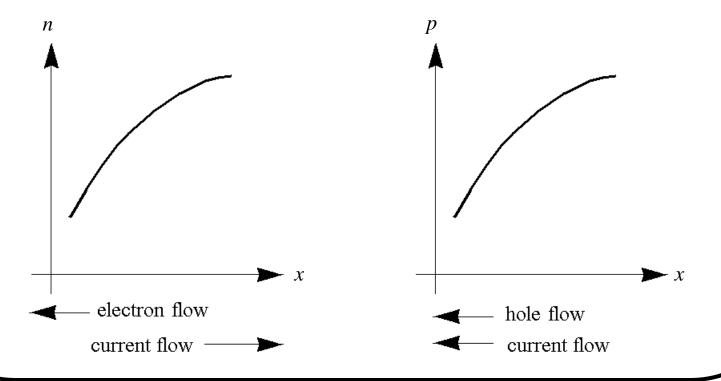

## 2.3 Diffusion Current

$$J_{n,diffusion} = qD_n \frac{dn}{dx}$$

$$J_{p,diffusion} = -qD_p \frac{dp}{dx}$$

D is called the diffusion constant. Signs explained:

## Total Current - Review of Four Current Components

$$J_{TOTAL} = J_n + J_p$$

$$J_n = J_{n,drift} + J_{n,diffusion} = qn\mu_n \mathbf{E} + qD_n \frac{dn}{dx}$$

$$J_p = J_{p,drift} + J_{p,diffusion} = qp\mu_p$$

E $- qD_p \frac{dp}{dx}$

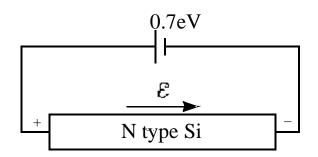

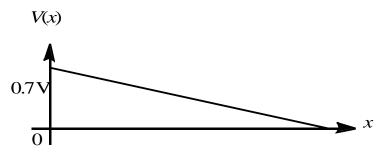

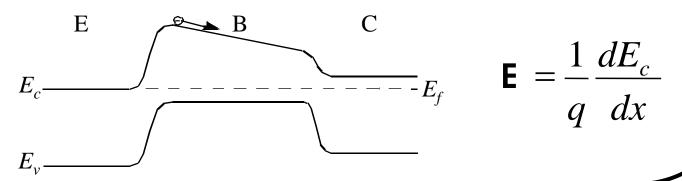

# 2.4 Relation Between the Energy Diagram and V, E

$E_c$  and  $E_v$  vary in the opposite direction from the voltage. That is,  $E_c$  and  $E_v$  are higher where the voltage is lower.

$$\mathbf{E}(x) = -\frac{dV}{dx} = \frac{1}{q} \frac{dE_c}{dx} = \frac{1}{q} \frac{dE_v}{dx}$$

## 2.5 Einstein Relationship between D and $\mu$

Consider a piece of non-uniformly doped semiconductor.

N-type semiconductor

Decreasing donor concentration

$$n = N_c e^{-(E_c - E_f)/kT}$$

$$\frac{dn}{dx} = -\frac{N_c}{kT}e^{-(E_c - E_f)/kT} \frac{dE_c}{dx}$$

$$E_c(x) = -\frac{n}{kT} \frac{dE_c}{dx}$$

$$=-\frac{n}{kT}q$$

$$E_{\nu}(x)$$

## 2.5 Einstein Relationship between D and $\mu$

$$\frac{dn}{dx} = -\frac{n}{kT}q\mathbf{E}$$

$$J_n = qn\mu_n \mathbf{E} + qD_n \frac{dn}{dx} = 0$$

at equilibrium.

$$0 = qn\mu_n \mathbf{E} - qn \frac{qD_n}{kT} \mathbf{E}$$

$$D_n = \frac{kT}{q} \mu_n$$

Similarly,  $D_p = \frac{kT}{q} \mu_p$

These are known as the Einstein relationship.

## EXAMPLE: Diffusion Constant

What is the hole diffusion constant in a piece of silicon with  $\mu_p = 410 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ ?

#### Solution:

$$D_p = \left(\frac{kT}{q}\right)\mu_p = (26 \text{ mV}) \cdot 410 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1} = 11 \text{ cm}^2/\text{s}$$

Remember: kT/q = 26 mV at room temperature.

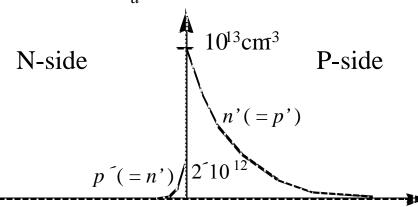

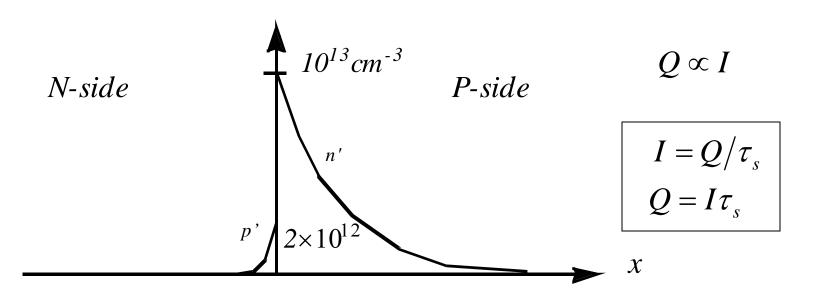

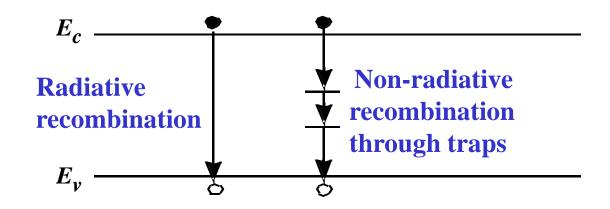

#### 2.6 Electron-Hole Recombination

- •The equilibrium carrier concentrations are denoted with  $n_0$  and  $p_0$ .

- •The total electron and hole concentrations can be different from  $n_0$  and  $p_0$ .

- The differences are called the *excess carrier* concentrations n' and p'.

$$n \equiv n_0 + n'$$

$$p \equiv p_0 + p'$$

## Charge Neutrality

- •Charge neutrality is satisfied at equilibrium (n'=p'=0).

- When a non-zero *n* 'is present, an equal *p* 'may be assumed to be present to maintain charge equality and vice-versa.

- •If charge neutrality is not satisfied, the net charge will attract or repel the (majority) carriers through the drift current until neutrality is restored.

$$n'=p'$$

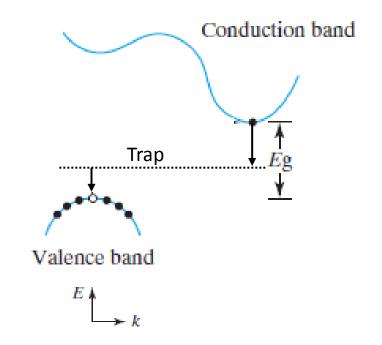

## Recombination Lifetime

- •Assume light generates n and p. If the light is suddenly turned off, n and p decay with time until they become zero.

- •The process of decay is called *recombination*.

- •The time constant of decay is the *recombination* time or carrier lifetime,  $\tau$ .

- •Recombination is nature's way of restoring equilibrium (n'=p'=0).

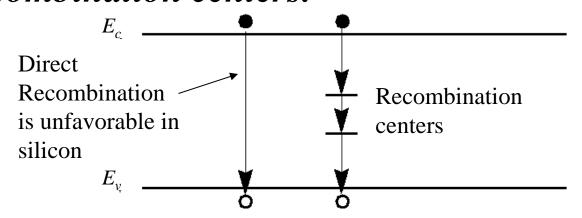

## Recombination Lifetime

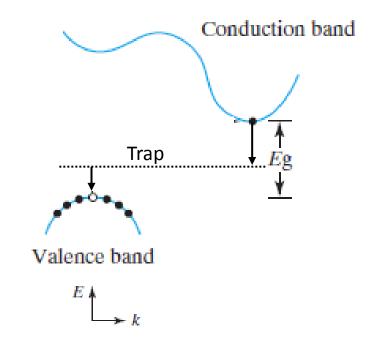

- τ ranges from 1ns to 1ms in Si and depends on the density of metal impurities (contaminants) such as Au and Pt.

- •These *deep traps* capture electrons and holes to facilitate recombination and are called *recombination centers*.

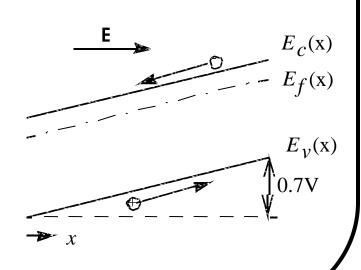

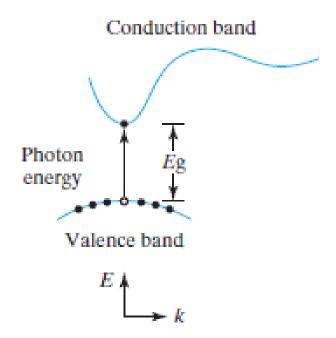

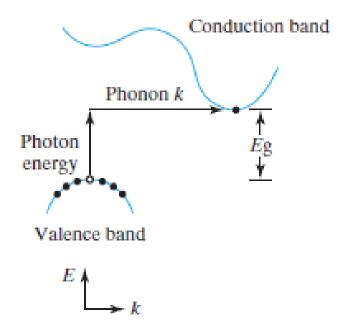

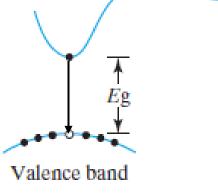

## Direct and Indirect Band Gap

Direct band gap Example: GaAs

Direct recombination is efficient as k conservation is satisfied.

Indirect band gap Example: Si

Direct recombination is rare as k conservation is not satisfied

## Rate of recombination (s<sup>-1</sup>cm<sup>-3</sup>)

$$\frac{dn'}{dt} = -\frac{n'}{\tau}$$

$$n'=p'$$

$$\frac{dn'}{dt} = -\frac{n'}{\tau} = -\frac{p'}{\tau} = \frac{dp'}{dt}$$

#### **EXAMPLE:** Photoconductors

A bar of Si is doped with boron at  $10^{15}$ cm<sup>-3</sup>. It is exposed to light such that electron-hole pairs are generated throughout the volume of the bar at the rate of  $10^{20}/\text{s}\cdot\text{cm}^3$ . The recombination lifetime is  $10\mu\text{s}$ . What are (a)  $p_0$ , (b)  $n_0$ , (c) p, (d) n, (e) p, (f) n, and (g) the np product?

#### **EXAMPLE:** Photoconductors

#### Solution:

- (a) What is  $p_0$ ?  $p_0 = N_a = 10^{15} \text{ cm}^{-3}$

- (b) What is  $n_0$ ?  $n_0 = n_i^2/p_0 = 10^5 \text{ cm}^{-3}$

- (c) What is p'?

In steady-state, the rate of generation is equal to the rate of recombination.

$$10^{20}/\text{s-cm}^3 = p'/\tau$$

$\therefore p' = 10^{20}/\text{s-cm}^3 \cdot 10^{-5}\text{s} = 10^{15} \text{ cm}^{-3}$

#### **EXAMPLE:** Photoconductors

- (d) What is n'?  $n' = p' = 10^{15} \text{ cm}^{-3}$

- (e) What is p?  $p = p_0 + p' = 10^{15} \text{cm}^{-3} + 10^{15} \text{cm}^{-3} = 2 \times 10^{15} \text{cm}^{-3}$

- (f) What is n?  $n = n_0 + n' = 10^5 \text{cm}^{-3} + 10^{15} \text{cm}^{-3} \sim 10^{15} \text{cm}^{-3} \text{ since } n_0 << n'$

- (g) What is np?  $np \sim 2 \times 10^{15} \text{cm}^{-3} \cdot 10^{15} \text{cm}^{-3} = 2 \times 10^{30} \text{ cm}^{-6} >> n_i^2 = 10^{20} \text{ cm}^{-6}.$  The np product can be very different from  $n_i^2$ .

#### 2.7 Thermal Generation

If n is negative, there are fewer electrons than the equilibrium value.

As a result, there is a net rate of *thermal generation* at the rate of  $|n'|/\tau$ .

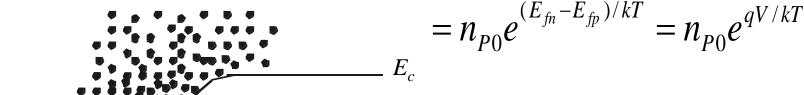

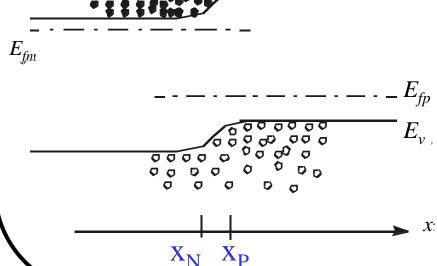

## 2.8 Quasi-equilibrium and Quasi-Fermi Levels

• Whenever  $n' = p' \neq 0$ ,  $np \neq n_i^2$ . We would like to preserve and use the simple relations:

$$n = N_c e^{-(E_c - E_f)/kT}$$

$$p = N_{\nu} e^{-(E_f - E_{\nu})/kT}$$

• But these equations lead to  $np = n_i^2$ . The solution is to introduce two *quasi-Fermi levels*  $E_{fn}$  and  $E_{fp}$  such that

$$n = N_c e^{-(E_c - E_{fn})/kT}$$

$$p = N_{\nu} e^{-(E_{fp} - E_{\nu})/kT}$$

Even when electrons and holes are not at equilibrium, within each group the carriers can be at equilibrium. Electrons are closely linked to other electrons but only loosely to holes.

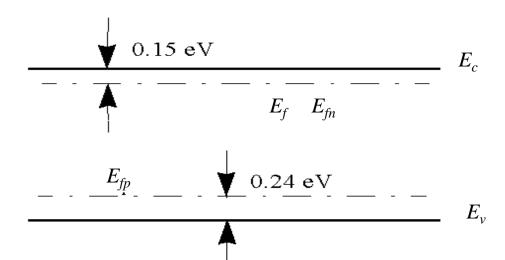

#### EXAMPLE: Quasi-Fermi Levels and Low-Level Injection

Consider a Si sample with  $N_d = 10^{17} \text{cm}^{-3}$  and  $n' = p' = 10^{15} \text{cm}^{-3}$ .

(a) Find

$$E_f$$

.

$n = N_d = 10^{17} \text{ cm}^{-3} = N_c \exp[-(E_c - E_f)/kT]$

$\therefore E_c - E_f = 0.15 \text{ eV}. \quad (E_f \text{ is below } E_c \text{ by } 0.15 \text{ eV}.)$

Note: n'and p'are much less than the majority carrier concentration. This condition is called low-level injection.

#### EXAMPLE: Quasi-Fermi Levels and Low-Level Injection

Now assume  $n' = p' = 10^{15} \text{ cm}^{-3}$ . (b) Find  $E_{fn}$  and  $E_{fp}$ .

$$n = 1.01 \times 10^{17} \text{cm}^{-3} = N_c e^{-(E_c - E_{fn})/kT}$$

$$\therefore E_c - E_{fn} = kT \times \ln(N_c/1.01 \times 10^{17} \text{cm}^{-3})$$

= 26 meV \times \ln(2.8 \times 10^{19} \text{cm}^{-3}/1.01 \times 10^{17} \text{cm}^{-3})

= 0.15 eV

$E_{fn}$  is nearly identical to  $E_f$  because  $n \approx n_0$ .

## EXAMPLE: Quasi-Fermi Levels

$$p = 10^{15} \,\mathrm{cm}^{-3} = N_{\nu} e^{-(E_{fp} - E_{\nu})/kT}$$

$$\therefore E_{fp} - E_v = kT \times \ln(N_v / 10^{15} \text{cm}^{-3})$$

= 26 meV \times \ln(1.04 \times 10^{19} \text{cm}^{-3} / 10^{15} \text{cm}^{-3})

= 0.24 eV

## 2.9 Chapter Summary

$$v_p = \mu_p \mathbf{E}$$

$v_n = -\mu_n \mathbf{E}$   $J_{p,drift} = qp\mu_p \mathbf{E}$   $J_{n,drift} = qn\mu_n \mathbf{E}$

$$J_{n,diffusion} = qD_n \frac{dn}{dx}$$

$$J_{p,diffusion} = -qD_p \frac{dp}{dx}$$

$$D_n = \frac{kT}{q} \mu_n$$

$$D_p = \frac{kT}{q} \mu_p$$

## 2.9 Chapter Summary

$\tau$  is the recombination lifetime. n and p are the excess carrier concentrations.

$$\begin{vmatrix} n = n_0 + n' \\ p = p_0 + p' \end{vmatrix}$$

Charge neutrality requires n' = p'.

rate of recombination =

$$n'/\tau = p'/\tau$$

$E_{fn}$  and  $E_{fp}$  are the quasi-Fermi levels of electrons and holes.

$$n = N_c e^{-(E_c - E_{fn})/kT}$$

$$p = N_v e^{-(E_{fp} - E_v)/kT}$$

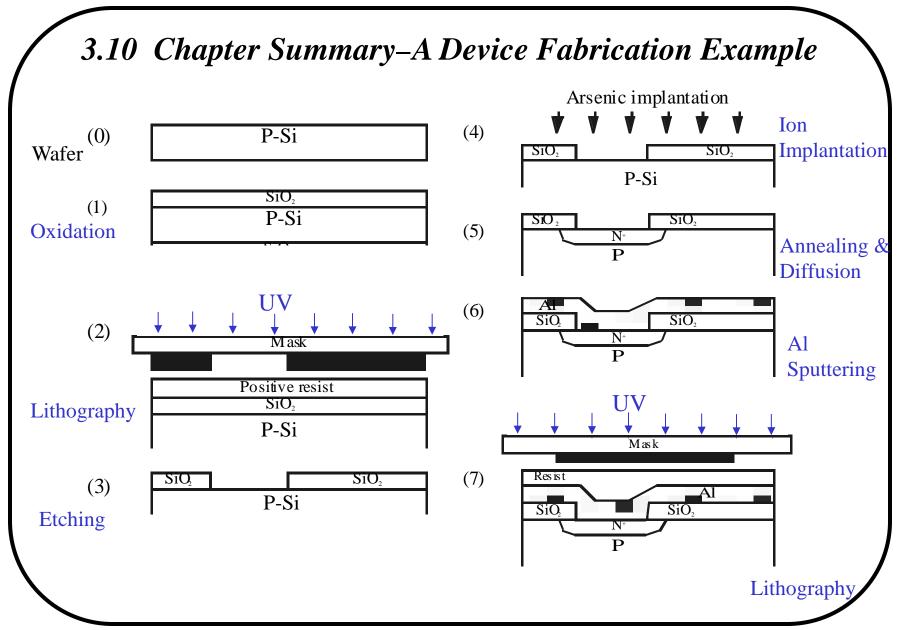

# Chapter 3 Device Fabrication Technology

About 10<sup>20</sup> transistors (or 10 billion for every person in the world) are manufactured every year.

VLSI (Very Large Scale Integration)

ULSI (Ultra Large Scale Integration)

GSI (Giga-Scale Integration)

Variations of this versatile technology are used for flat-panel displays, micro-electro-mechanical systems (*MEMS*), and chips for DNA screening...

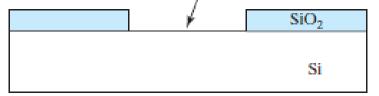

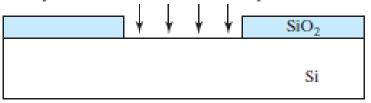

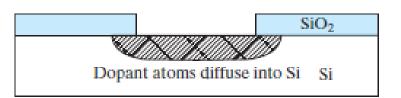

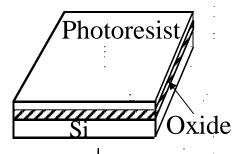

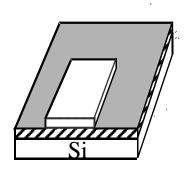

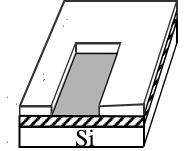

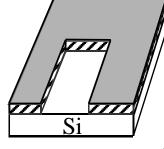

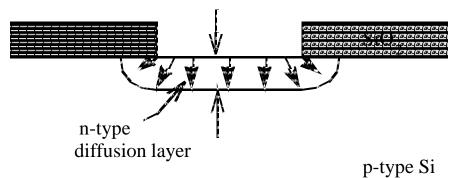

#### 3.1 Introduction to Device Fabrication

Oxidation

SiO<sub>2</sub>

Lithography & Etching

SiO2 selectively etched

Ion Implantation

Dopant atoms introduced into exposed silicon

Annealing & Diffusion

## 3.2 Oxidation of Silicon

Dry Oxidation :  $Si + O_2 \rightarrow SiO_2$

Wet Oxidation :  $Si + 2H_2O \rightarrow SiO_2 + 2H_2$

## 3.2 Oxidation of Silicon

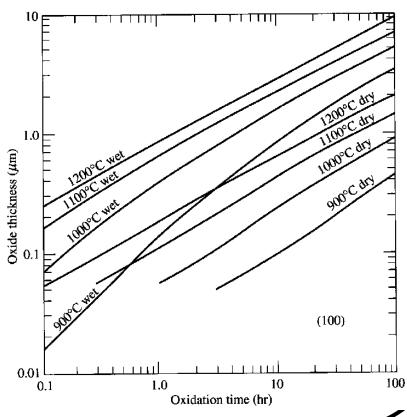

#### EXAMPLE: Two-step Oxidation

- (a) How long does it take to grow 0.1 \mu of dry oxide at 1000 °C?

- (b) After step (a), how long will it take to grow an additional  $0.2 \mu m$  of oxide at  $900 \, ^{\circ}C$  in a wet ambient?

#### Solution:

- (a) From the "1000°C dry" curve in Slide 3-3, it takes 2.5 hr to grow 0.1 µm of oxide.

- (b) Use the "900°C wet" curve only. It would have taken 0.7hr to grow the 0.1  $\mu$ m oxide and 2.4hr to grow 0.3  $\mu$ m oxide from bare silicon. The answer is 2.4hr–0.7hr = 1.7hr.

(a) Resist Coating

(b) Exposure

Positive resist N

Negative resist

Deep Ultraviolet Light

Optical Lens system

Photomask with opaque and clear patterns

(d) Etching and Resist Strip

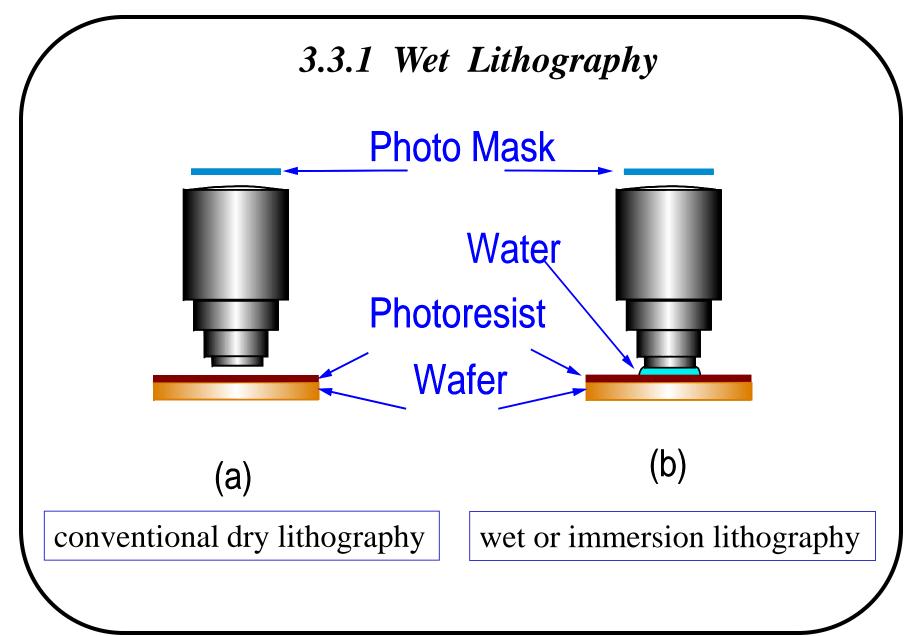

## 3.3 Lithography

#### Photolithography Resolution Limit, R

- $R \ge k\lambda$  due to optical diffraction

- Wavelength  $\lambda$  needs to be minimized. (248 nm, 193 nm, 157 nm?)

- k (<1) can be reduced will

- Large aperture, high quality lens

- Small exposure field, step-and-repeat using "stepper"

- Optical proximity correction

- Phase-shift mask, etc.

- Lithography is difficult and expensive. There can be 40 lithography steps in an IC process.

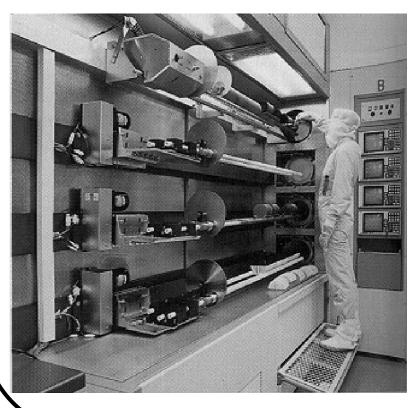

## 3.3 Lithography

Wafers are being loaded into a stepper in a clean room.

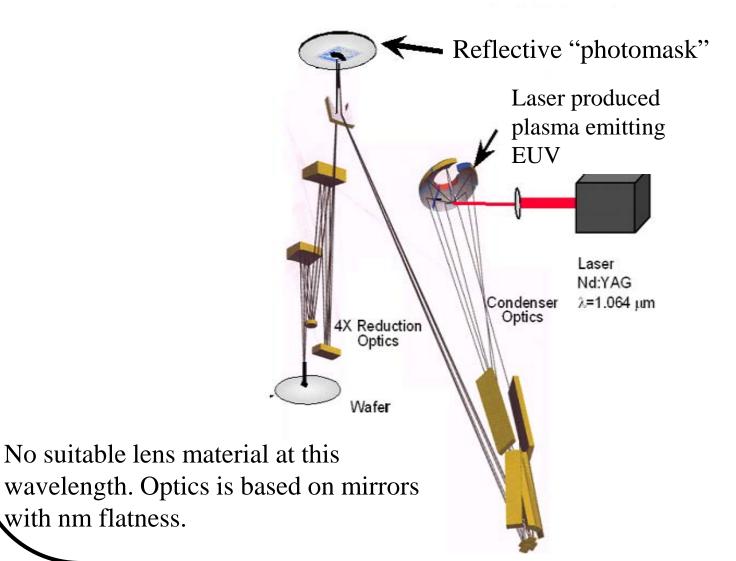

## Extreme UV Lithography (13nm wavelength)

with nm flatness.

## Beyond Optical Lithography

- *Electron Beam Writing*: Electron beam(s) scans and exposed electron resist on wafer. Ready technology with relatively low throughput.

- *Electron Projection Lithography*: Exposes a complex pattern using mask and electron lens similar to optical lithography.

- *Nano-imprint*: Patterns are etched into a durable material to make a "stamp." This stamp is pressed into a liquid film over the wafer surface. Liquid is hardened with UV to create an imprint of the fine patterns.

## 3.4 Pattern Transfer-Etching

## **Isotropic etching Anisotropic etching** photoresist photoresist SiO SiO photoresist photoresist SiO Si ũΟ

## 3.4 Pattern Transfer-Etching

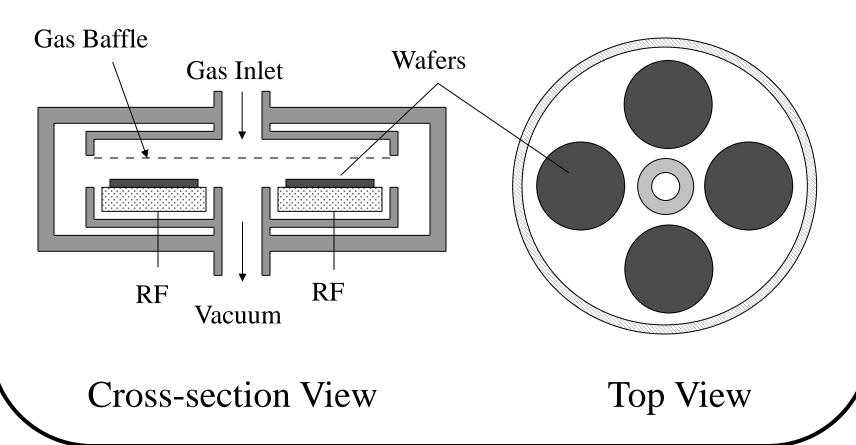

#### Reactive-Ion Etching Systems

## 3.4 Pattern Transfer-Etching

Dry Etching (also known as Plasma Etching, or Reactive-Ion Etching) is anisotropic.

- Silicon and its compounds can be etched by plasmas containing F.

- Aluminum can be etched by Cl.

- Some concerns:

- Selectivity and End-Point Detection

- Plasma Process-Induced Damage or Wafer Charging Damage and Antenna Effect

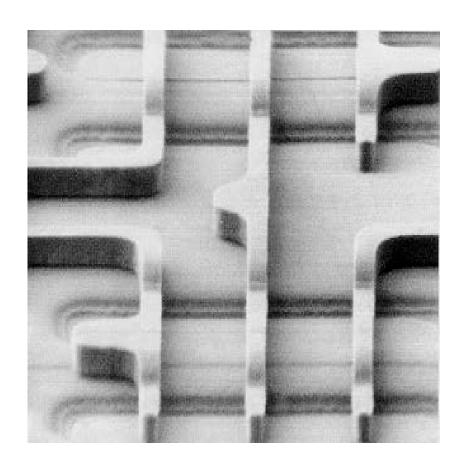

# Scanning electron microscope view of a plasma-etched 0.16 µm pattern in polycrystalline silicon film.

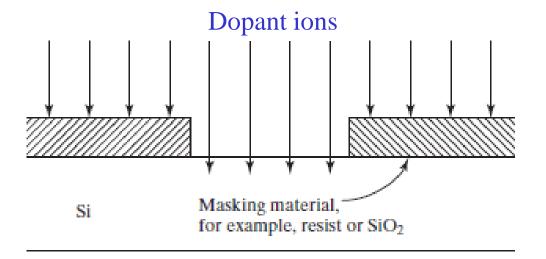

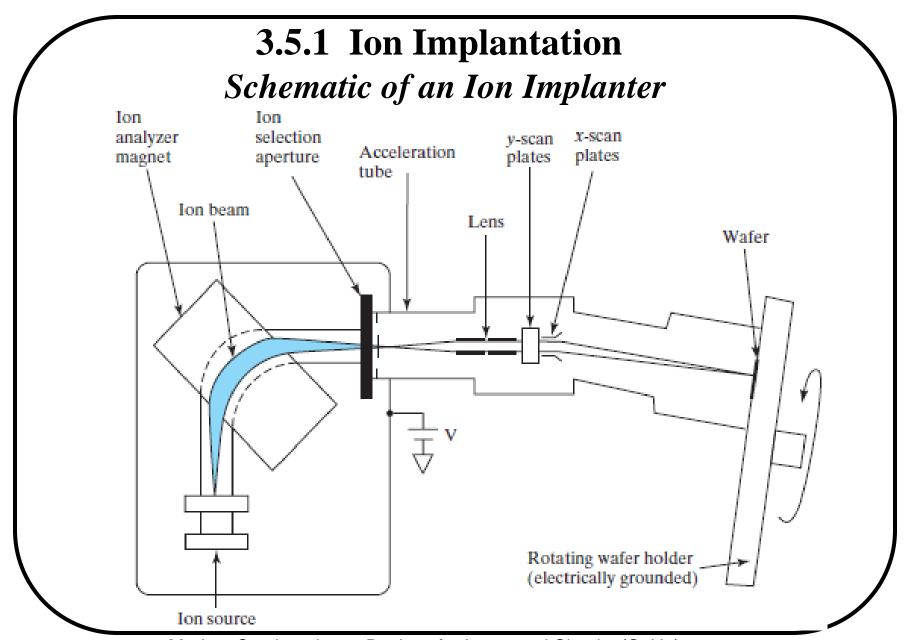

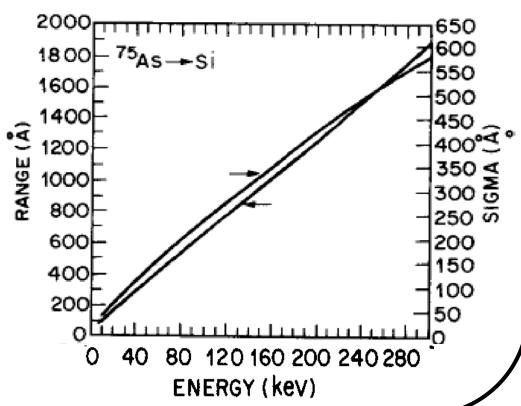

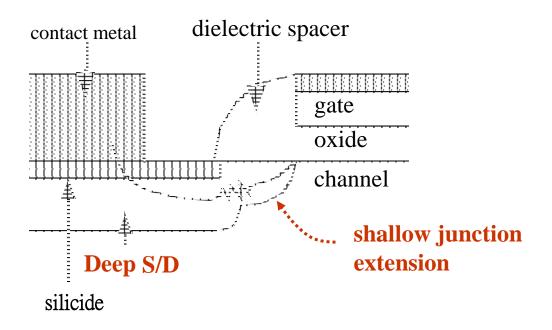

# 3.5 Doping3.5.1 Ion Implantation

- The dominant doping method

- Excellent control of **dose** (cm<sup>-2</sup>)

- Good control of implant depth with energy (KeV to MeV)

- Repairing crystal damage and dopant activation requires annealing, which can cause dopant diffusion and loss of depth control.

## 3.5.1 Ion implantation

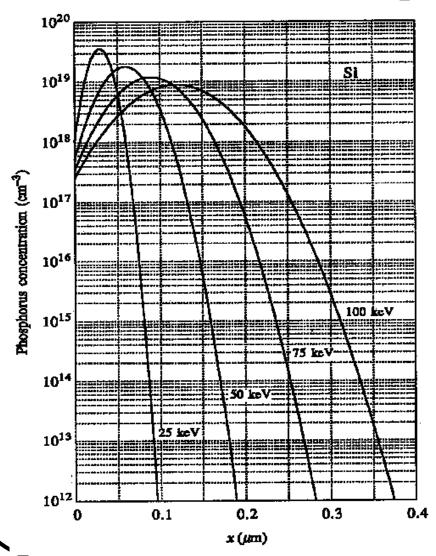

Phosphorous density profile after implantation

## 3.5.1 Ion Implantation

Model of Implantation Doping Profile (Gaussian)

$$N(x) = \frac{N_i}{\sqrt{2\pi} \cdot (\Delta R)} \cdot e^{-(x-R)^2/2\Delta R^2}$$

$N_i$ : dose (cm<sup>-2</sup>)

R : range or depth

$\Delta R$ : spread or sigma

#### Other Doping Methods

- *Gas-Source Doping*: For example, dope Si with P using POCl<sub>3</sub>.

- *Solid-Source Doping*: Dopant diffuses from a doped solid film (SiGe or oxide) into Si.

- *In-Situ Doping*: Dopant is introduced while a Si film is being deposited.

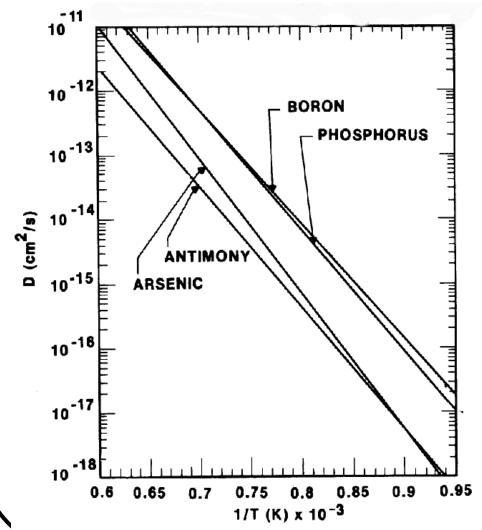

## 3.6 Dopant Diffusion

Junction depth

$$N(x,t) = \frac{N_o}{\sqrt{\pi \cdot Dt}} e^{-x^2/4Dt}$$

$N: N_d \text{ or } N_a \text{ (cm}^{-3})$

$N_o$ : dopant atoms per cm<sup>2</sup>

t: diffusion time

D: diffusivity,  $\sqrt{Dt}$  is the approximate distance of

dopant diffusion

## 3.6 Dopant Diffusion

- *D* increases with increasing temperature.

- Some applications need very deep junctions (high T, long t). Others need very shallow junctions (low T, short t).

## 3.6 Dopant Diffusion

#### Shallow Junction and Rapid Thermal Annealing

- After ion implantation, thermal annealing is required. Furnace annealing takes minutes and causes too much diffusion of dopants for some applications.

- In rapid thermal annealing (RTA), the wafer is heated to high temperature in seconds by a bank of heat lamps.

- •In flash annealing (100mS) and laser annealing (<1uS), dopant ddiffusion is practically eliminated.

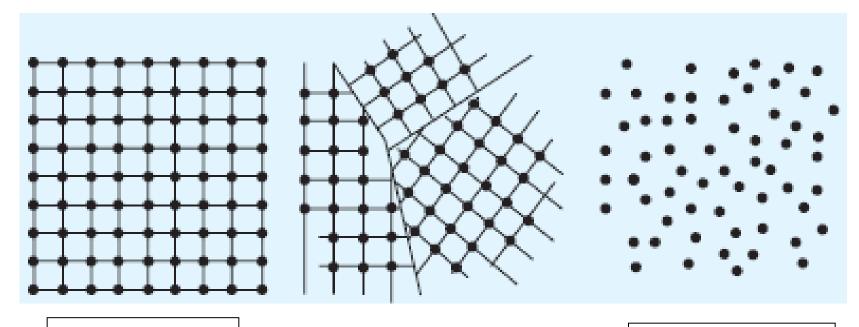

# 3.7 Thin-Film Deposition Three Kinds of Solid

Crystalline

Polycrystalline

Amorphous

Example: Silicon wafer

Thin film of Si or metal.

Thin film of SiO<sub>2</sub> or Si<sub>3</sub>N<sub>4</sub>.

## 3.7 Thin-Film Deposition

Examples of thin films in integrated circuits

- Advanced MOSFET gate dielectric

- Poly-Si film for transistor gates

- Metal layers for interconnects

- Dielectric between metal layers

- Encapsulation of IC

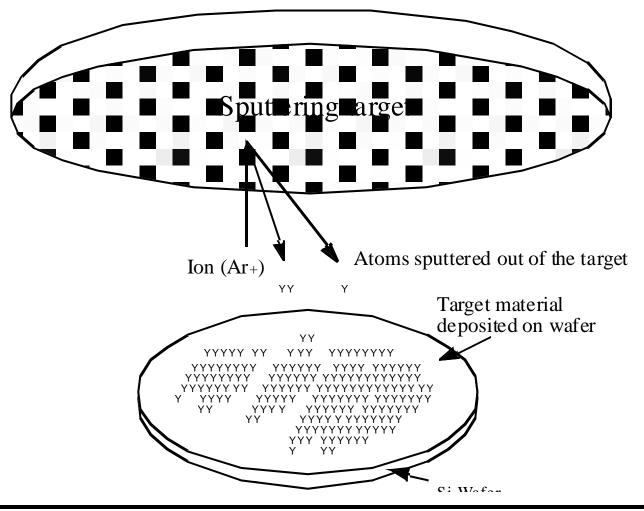

#### 3.7.1 Sputtering

#### Schematic Illustration of Sputtering Process

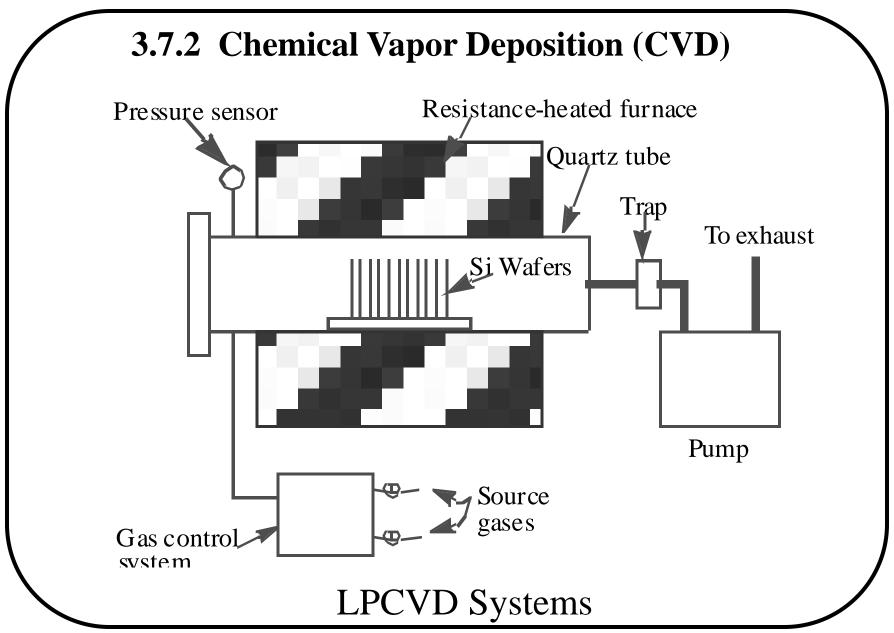

#### 3.7.2 Chemical Vapor Deposition (CVD)

Thin film is formed from gas phase components.

#### Some Chemical Reactions of CVD

Poly-Si:

$$SiH_4(g) \longrightarrow Si(s) + 2H_2(g)$$

Si3N4:

$$3SiH_2Cl_2(g)+4NH_3(g) \longrightarrow Si_3N_4(s)+6HCl(g)+6H_2(g)$$

SiO2: SiH<sub>4</sub> (g) + O<sub>2</sub> (g)

$$\longrightarrow$$

SiO<sub>2</sub> (s) + 2H<sub>2</sub> (g)

or

$$SiH_2Cl_2(g)+2N_2O(g) \longrightarrow SiO_2(s)+2HCl(g)+2N_2(g)$$

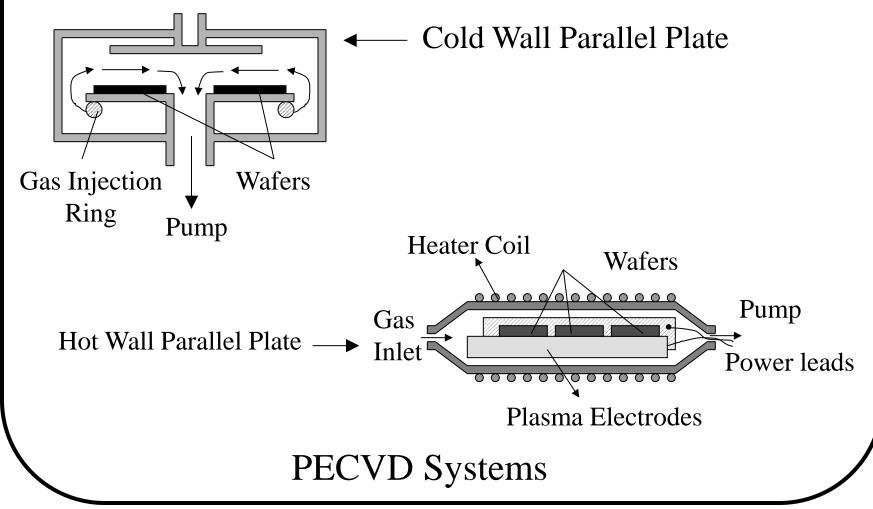

#### 3.7.2 Chemical Vapor Deposition (CVD)

Two types of CVD equipment:

- LPCVD (Low Pressure CVD): Good uniformity. Used for poly-Si, oxide, nitride.

- **PECVD** (**Plasma Enhanced CVD**): Low temperature process and high deposition rate. Used for oxide, nitride, etc.

#### 3.7.2 Chemical Vapor Deposition (CVD)

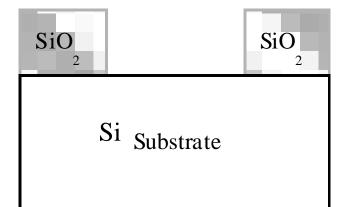

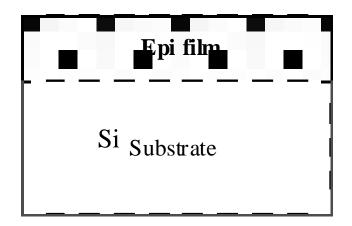

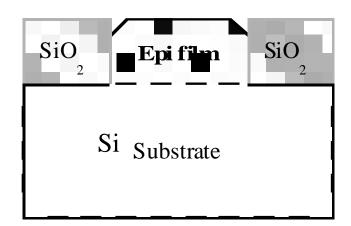

## 3.7.3 Epitaxy (Deposition of Single-Crystalline Film)

**Epitaxy**

Selective Epitaxy

Si <sub>Substrate</sub>

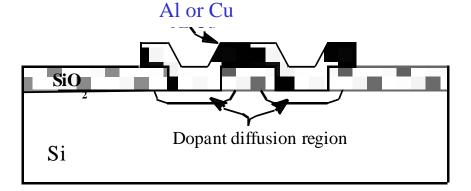

#### 3.8 Interconnect - The Back-end Process

Encapsulation

Dielectric

Dielectric

Silicide

2

diffusion region

Si

(b)

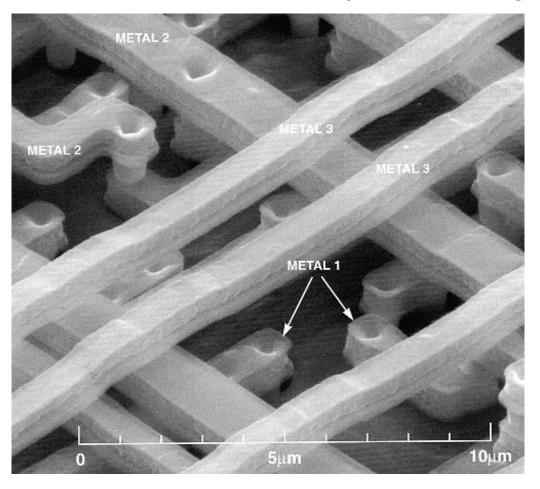

#### 3.8 Interconnect - The Back-end Process

SEM: Multi-Level Interconnect (after removing the dielectric)

#### 3.8 Interconnect – The Back-end Process

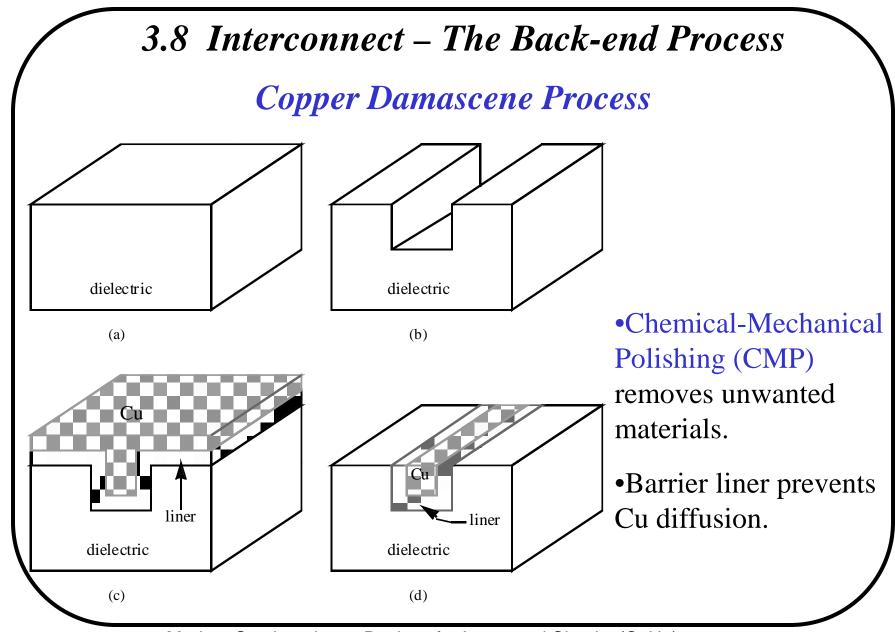

## Copper Interconnect

- Al interconnect is prone to voids formation by electromigration.

- Cu has excellent electromigration reliability and 40% lower resistance than Al.

- Because dry etching of copper is difficult (copper etching products tend to be non-volatile), copper patterns are defined by a *damascene* process.

#### 3.8 Interconnect - The Back-end Process

#### **Planarization**

- A flat surface is highly desirable for subsequent lithography and etching.

- CMP (Chemical-Mechanical Polishing) is used to planarize each layer of dielectric in the interconnect system. Also used in the front-end process.

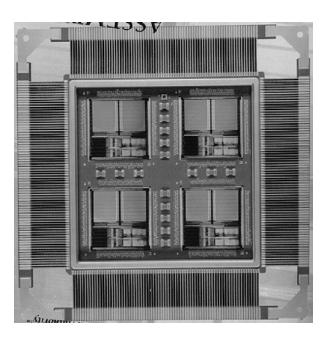

# 3.9 Testing, Assembly, and Qualification

- Wafer acceptance test

- Die sorting

- Wafer sawing or laser cutting

- Packaging

- Flip-chip solder bump technology

- Multi-chip modules

- Burn-in

- Final test

- Qualification

#### 3.10 Chapter Summary-A Device Fabrication Example Al (8) Metal SiO<sub>2</sub> SiO<sub>2</sub> (12)Back side etching metallization SiO S<sub>1</sub>O<sub>2</sub> (9) **CVD** nitride S1O, Au deposition $\overline{\mathbf{P}}$ wire (10)(13)Lithography Al S1O<sub>2</sub> and etching S1O<sub>2</sub> S<sub>1</sub>O<sub>2</sub> S<sub>1</sub>O<sub>2</sub> (11)Photoresist Au Plastic package **Back Side** metal leads milling SIU SiO Dicing, wire bonding, and packaging

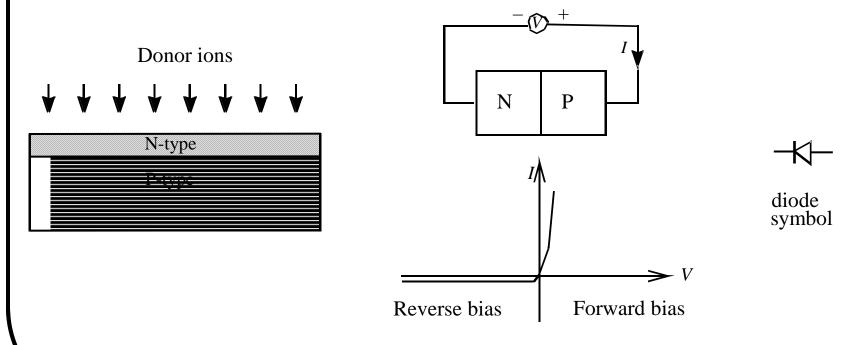

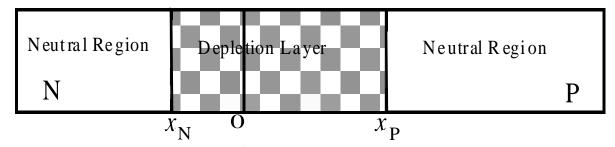

# Chapter 4 PN and Metal-Semiconductor Junctions

#### 4.1 Building Blocks of the PN Junction Theory

PN junction is present in perhaps every semiconductor device.

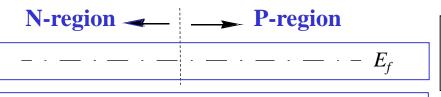

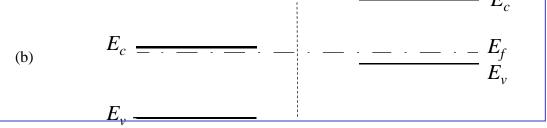

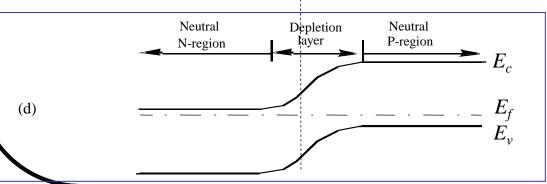

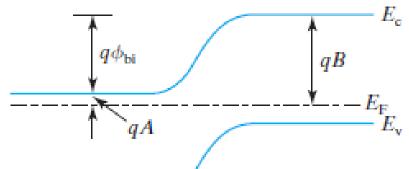

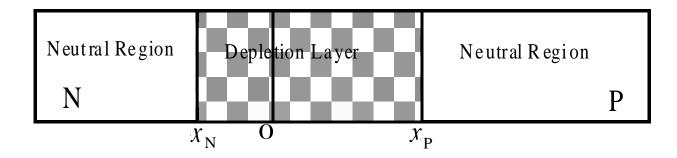

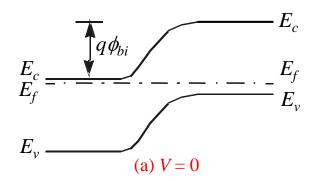

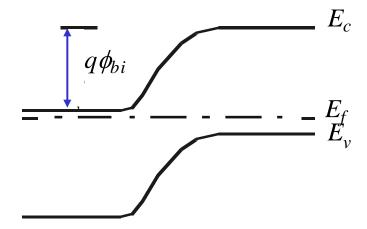

#### 4.1.1 Energy Band Diagram of a PN Junction

E<sub>f</sub> is constant at equilibrium

(a)

$E_c$  and  $E_v$  are known relative to  $E_f$

$E_c$  and  $E_v$  are smooth, the exact shape to be determined.

A depletion layer exists at the PN junction where  $n \approx 0$  and  $p \approx 0$ .

Can the built-in potential be measured with a voltmeter?

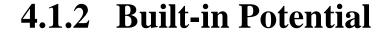

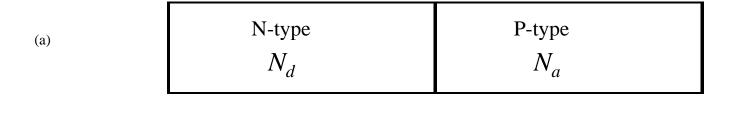

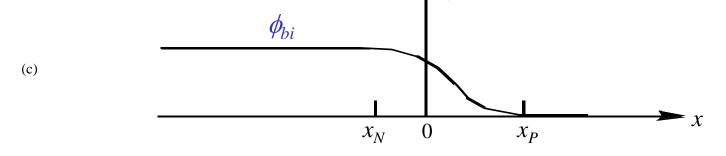

#### 4.1.2 Built-in Potential

N-region

$$n = N_d = N_c e^{-qA/kT} \Rightarrow A = \frac{kT}{q} \ln \frac{N_c}{N_d}$$

P-region

$$n = \frac{n_i^2}{N_a} = N_c e^{-qB/kT} \Rightarrow B = \frac{kT}{q} \ln \frac{N_c N_a}{n_i^2}$$

$$\phi_{bi} = B - A = \frac{kT}{q} \left( \ln \frac{N_c N_a}{n_i^2} - \ln \frac{N_c}{N_d} \right)$$

$$\phi_{bi} = \frac{kT}{q} \ln \frac{N_d N_a}{n_i^2}$$

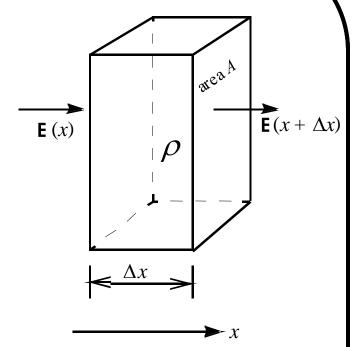

## 4.1.3 Poisson's Equation

#### Gauss's Law:

$$\varepsilon_{s} \mathcal{E}(x + \Delta x) A - \varepsilon_{s} \mathcal{E}(x) A = \rho \Delta x A$$

$\varepsilon_s$ : permittivity (~12 $\varepsilon_o$  for Si)

$\rho$ : charge density (C/cm<sup>3</sup>)

$$\frac{\mathcal{E}(x + \Delta x) - \mathcal{E}(x)}{\Delta x} = \frac{\rho}{\varepsilon_s}$$

$$\frac{d^2V}{dx^2} = -\frac{d\mathcal{E}}{dx} = -\frac{\rho}{\varepsilon_s}$$

Poisson's equation

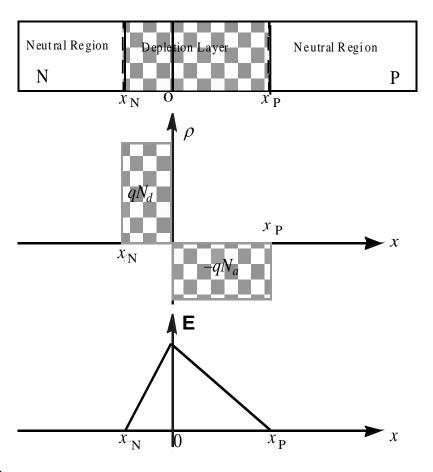

## 4.2 Depletion-Layer Model

#### 4.2.1 Field and Potential in the Depletion Layer

On the *P***-side** of the depletion layer,  $\rho = -qN_a$

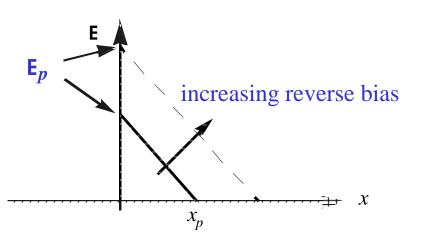

$$\frac{d\mathbf{E}}{dx} = -\frac{qN_a}{\varepsilon_s}$$

$$\mathbf{E}(x) = -\frac{qN_a}{\varepsilon_s} x + C_1 = \boxed{\frac{qN_a}{\varepsilon_s} (x_P - x)}$$

On the *N*-side,  $\rho = qN_d$

$$\mathbf{E}(x) = \frac{qN_d}{\varepsilon_s}(x - x_{\rm N})$$

## 4.2.1 Field and Potential in the Depletion Layer

The electric field is continuous at x = 0.

$$N_a/x_{\rm P}/=N_d/x_{\rm P}/$$

Which side of the junction is depleted more?

A one-sided junction is called a  $N^+P$  junction or  $P^+N$  junction

#### 4.2.1 Field and Potential in the Depletion Layer

On the P-side,

$$V(x) = \frac{qN_a}{2\varepsilon_s}(x_P - x)^2$$

Arbitrarily choose the voltage at  $x = x_P$  as V = 0.

On the N-side,

$$V(x) = D - \frac{qN_d}{2\varepsilon_s} (x - x_N)^2$$

$$= \phi_{bi} - \frac{qN_d}{2\varepsilon_s} (x - x_N)^2$$

## 4.2.2 Depletion-Layer Width

*V* is continuous at x = 0

$$x_{P} - x_{N} = W_{dep} = \sqrt{\frac{2\varepsilon_{s}\phi_{bi}}{q} \left(\frac{1}{N_{a}} + \frac{1}{N_{d}}\right)}$$

If  $N_a >> N_d$ , as in a P+N junction,

$$W_{dep} = \sqrt{\frac{2\varepsilon_s \phi_{bi}}{qN_d}} \approx \left| x_N \right|$$

$$/x_P/=/x_N/N_d/N_a\cong 0$$

What about a N+P junction?

$$W_{dep} = \sqrt{2\varepsilon_s \, \phi_{bi}/qN}$$

where  $\frac{1}{N} = \frac{1}{N_d} + \frac{1}{N_a} \approx \frac{1}{lighter\ dopant\ density}$

**EXAMPLE**: A  $P^+N$  junction has  $N_a=10^{20}$  cm<sup>-3</sup> and  $N_d=10^{17}$ cm<sup>-3</sup>. What is a) its built in potential, b) $W_{dep}$ , c) $x_N$ , and d)  $x_P$ ?

#### Solution:

a)

$$\phi_{bi} = \frac{kT}{q} \ln \frac{N_d N_a}{n_i^2} = 0.026 \text{V} \ln \frac{10^{20} \times 10^{17} \text{ cm}^{-6}}{10^{20} \text{ cm}^{-6}} \approx 1 \text{ V}$$

b)

$$W_{dep} \approx \sqrt{\frac{2\varepsilon_s \phi_{bi}}{qN_d}} = \left(\frac{2 \times 12 \times 8.85 \times 10^{-14} \times 1}{1.6 \times 10^{-19} \times 10^{17}}\right)^{1/2} = 0.12 \,\mu\text{m}$$

c)

$$|x_N| \approx W_{dep} = 0.12 \,\mu\text{m}$$

$$|a| |x_P| = |x_N| N_d / N_a = 1.2 \times 10^{-4} \mu \text{m} = 1.2 \text{ Å} \approx 0$$

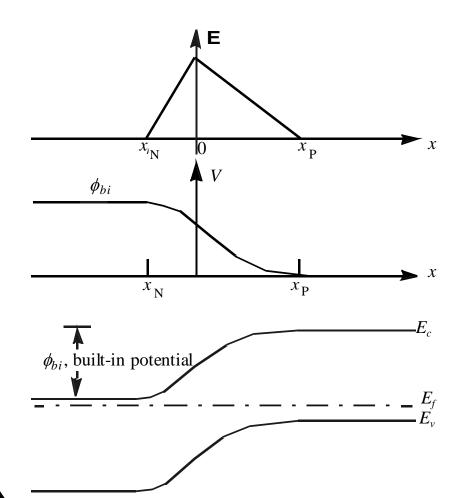

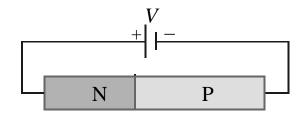

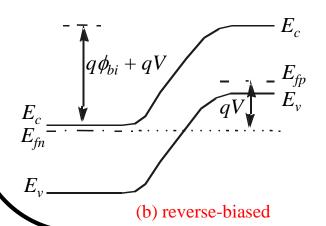

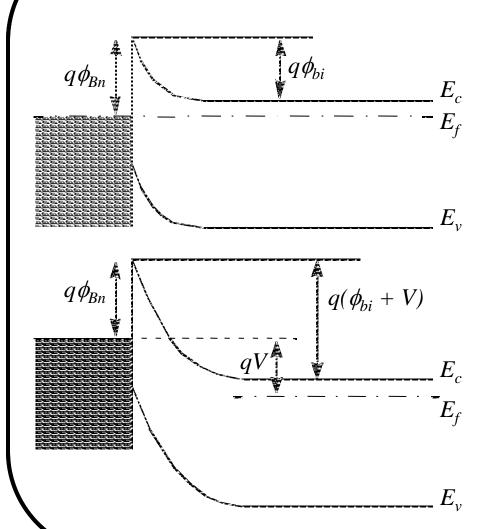

#### 4.3 Reverse-Biased PN Junction

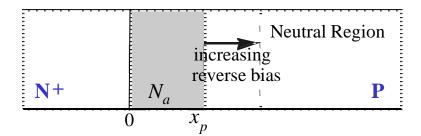

$$W_{dep} = \sqrt{\frac{2\varepsilon_{s}(\phi_{bi} + |V_{r}|)}{qN}} = \sqrt{\frac{2\varepsilon_{s} \cdot potential\ barrier}{qN}}$$

$$\frac{1}{N} = \frac{1}{N_d} + \frac{1}{N_a} \approx \frac{1}{lighter\ dopant\ density}$$

• Does the depletion layer widen or shrink with increasing reverse bias?

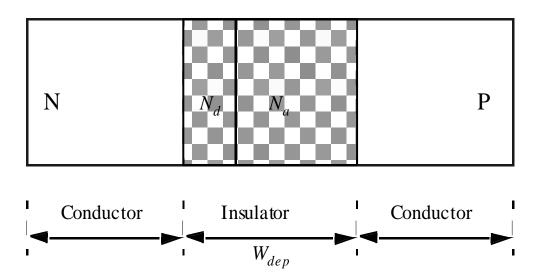

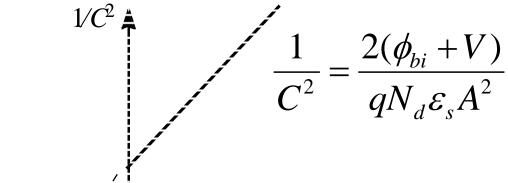

# 4.4 Capacitance-Voltage Characteristics

Reverse biased PN junction is a capacitor.

$$C_{dep} = A \frac{\mathcal{E}_s}{W_{dep}}$$

- Is  $C_{dep}$  a good thing?

- How to minimize junction capacitance?

# 4.4 Capacitance-Voltage Characteristics

$$\frac{1}{C_{dep}^{\ 2}} = \frac{W_{dep}^{\ 2}}{A^2 \varepsilon_s^{\ 2}} = \frac{2(\phi_{bi} + V)}{qN \varepsilon_s A^2}$$

$$\frac{1}{Q_{dep}^{\ 2}} = \frac{2(\phi_{bi} + V)}{qN \varepsilon_s A^2}$$

Slope =  $2/qN \varepsilon_s A^2$

$$V_r$$

Increasing reverse bias

• From this C-V data can  $N_a$  and  $N_d$  be determined?

**EXAMPLE:** If the slope of the line in the previous slide is  $2x10^{23} F^{-2} V^{-1}$ , the intercept is 0.84V, and A is 1  $\mu$ m<sup>2</sup>, find the lighter and heavier doping concentrations  $N_l$  and  $N_h$ .

#### **Solution:**

$$N_{l} = 2/(slope \times q\varepsilon_{s}A^{2})$$

$$= 2/(2\times10^{23}\times1.6\times10^{-19}\times12\times8.85\times10^{-14}\times10^{-8}\text{cm}^{2})$$

$$= 6\times10^{15} \text{ cm}^{-3}$$

$$\phi_{bi} = \frac{kT}{q} \ln \frac{N_h N_l}{n_i^2} \implies N_h = \frac{n_i^2}{N_l} e^{\frac{q\phi_{bi}}{kT}} = \frac{10^{20}}{6 \times 10^{15}} e^{\frac{0.84}{0.026}} = 1.8 \times 10^{18} \text{ cm}^{-3}$$

• Is this an accurate way to determine  $N_1$ ?  $N_h$ ?

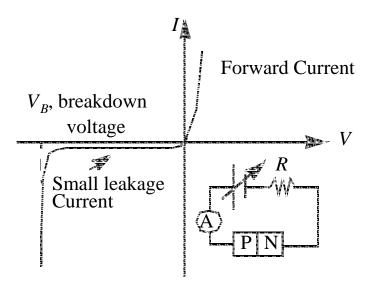

#### 4.5 Junction Breakdown

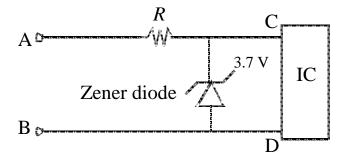

A Zener diode is designed to operate in the breakdown mode.

#### 4.5.1 Peak Electric Field

$$\mathbf{E}_{p} = \mathbf{E}(0) = \left[\frac{2qN}{\varepsilon_{s}}(\phi_{bi} + |V_{r}|)\right]^{1/2}$$

$$V_{B} = \frac{\varepsilon_{s} \mathbf{E}_{crit}^{2}}{2qN} - \phi_{bi}$$

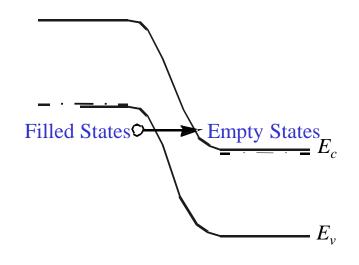

## 4.5.2 Tunneling Breakdown

Dominant if both sides of a junction are very heavily doped.

$$J = G e^{-H/\mathcal{E}_p}$$

$$\mathbf{E}_{p} = \mathbf{E}_{crit} \approx 10^6 \text{ V/cm}$$

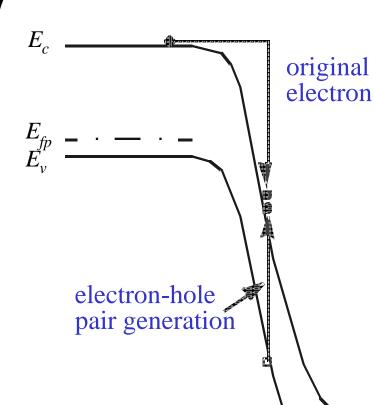

- *impact ionization*: an energetic electron generating electron and hole, which can also cause impact ionization.

- Impact ionization + positive feedback → avalanche breakdown

$$V_{B} = \frac{\mathcal{E}_{s} \mathbf{E}_{crit}^{2}}{2qN}$$

$$egin{aligned} E_c \ E_{fn} \end{aligned}$$

$$|V_B| \propto \frac{1}{N} = \frac{1}{N_a} + \frac{1}{N_d}$$

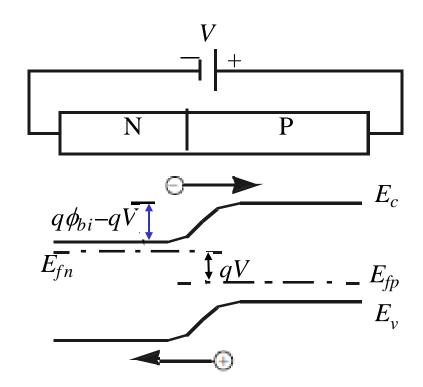

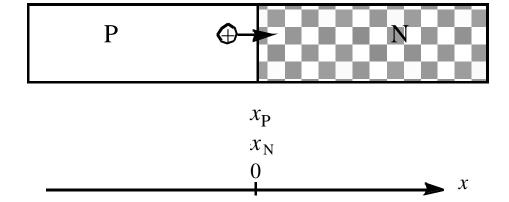

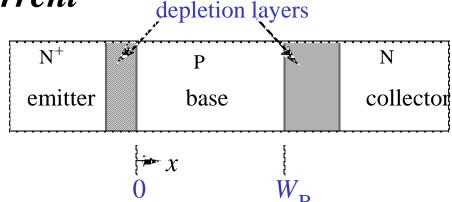

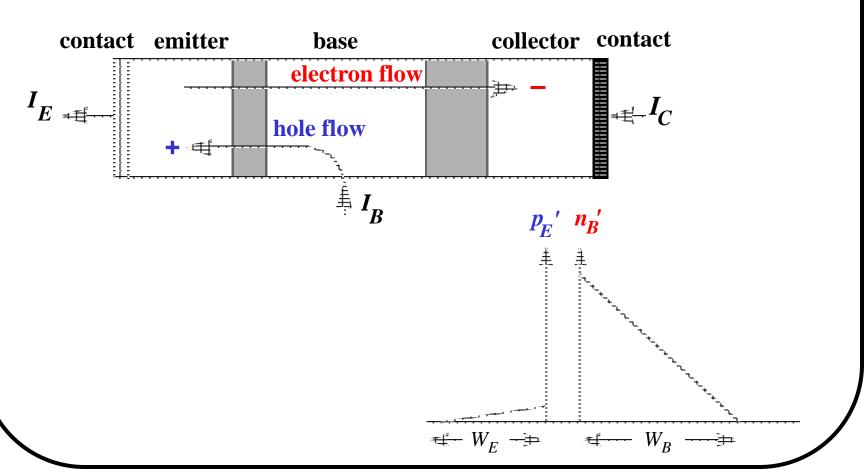

# 4.6 Forward Bias – Carrier Injection

$$I=0$$

Drift and diffusion cancel out

#### Forward biased

Minority carrier injection

# 4.6 Forward Bias – Quasi-equilibrium Boundary Condition

$$n(x_{\rm P}) = N_c e^{-(E_c - E_{fn})/kT} = N_c e^{-(E_c - E_{fp})/kT} e^{(E_{fn} - E_{fp})/kT}$$

- The minority carrier densities are raised by  $e^{qV/kT}$

- Which side gets more carrier injection?

# 4.6 Carrier Injection Under Forward Bias-Quasi-equilibrium Boundary Condition

$$n(x_P) = n_{P0}e^{qV/kT} = \frac{n_i^2}{N_a}e^{qV/kT}$$

$$p(x_P) = p_{N0}e^{qV/kT} = \frac{n_i^2}{N_d}e^{qV/kT}$$

$$n'(x_P) \equiv n(x_P) - n_{P0} = n_{P0}(e^{qV/kT} - 1)$$

$$p'(x_N) \equiv p(x_N) - p_{N0} = p_{N0}(e^{qV/kT} - 1)$$

# EXAMPLE: Carrier Injection

A PN junction has  $N_a$ =10<sup>19</sup>cm<sup>-3</sup> and  $N_d$ =10<sup>16</sup>cm<sup>-3</sup>. The applied voltage is 0.6 V.

**Question**: What are the minority carrier concentrations at the depletion-region edges?

**Solution:**

$$n(x_P) = n_{P0}e^{qV/kT} = 10 \times e^{0.6/0.026} = 10^{11} \text{ cm}^{-3}$$

$p(x_N) = p_{N0}e^{qV/kT} = 10^4 \times e^{0.6/0.026} = 10^{14} \text{ cm}^{-3}$

Question: What are the excess minority carrier concentrations?

**Solution:**

$$n'(x_P) = n(x_P) - n_{P0} = 10^{11} - 10 = 10^{11} \text{ cm}^{-3}$$

$p'(x_N) = p(x_N) - p_{N0} = 10^{14} - 10^4 = 10^{14} \text{ cm}^{-3}$

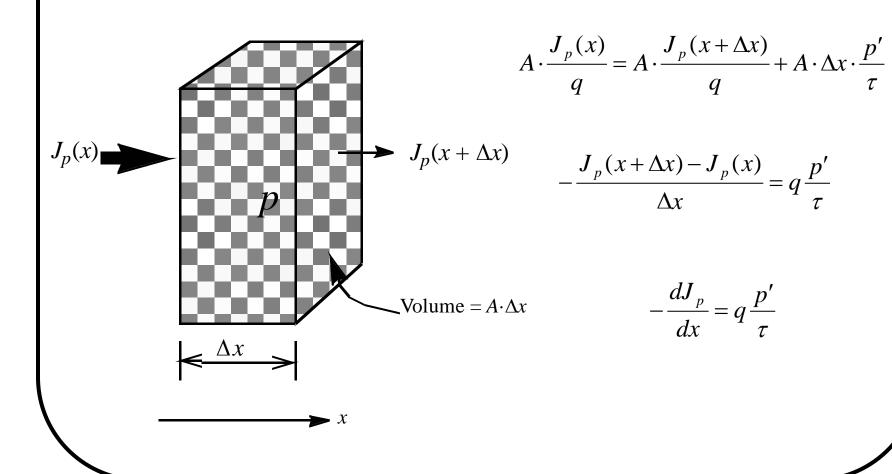

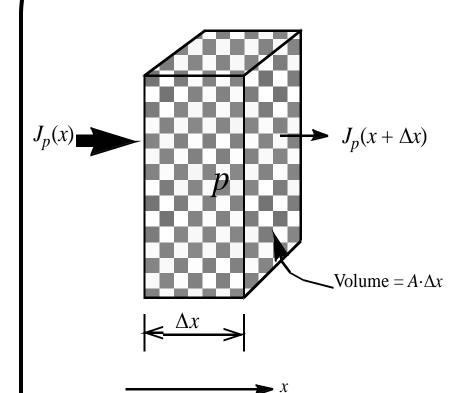

# 4.7 Current Continuity Equation

# 4.7 Current Continuity Equation

$$-\frac{dJ_p}{dx} = q\frac{p'}{\tau}$$

Minority drift current is negligible;

$$\therefore J_p = -qD_p dp/dx$$

$$qD_p \frac{d^2p}{dx^2} = q \frac{p'}{\tau_p}$$

$$qD_p \frac{d^2p}{dx^2} = q \frac{p'}{\tau_p}$$

$$\frac{d^2p'}{dx^2} = \frac{p'}{D_p\tau_p} = \frac{p'}{L_p^2}$$

$$\frac{d^2n'}{dx^2} = \frac{n'}{L_n^2}$$

$L_p$  and  $L_n$  are the diffusion lengths

$$L_p \equiv \sqrt{D_p \tau_p}$$

$$L_n \equiv \sqrt{D_n \tau_n}$$

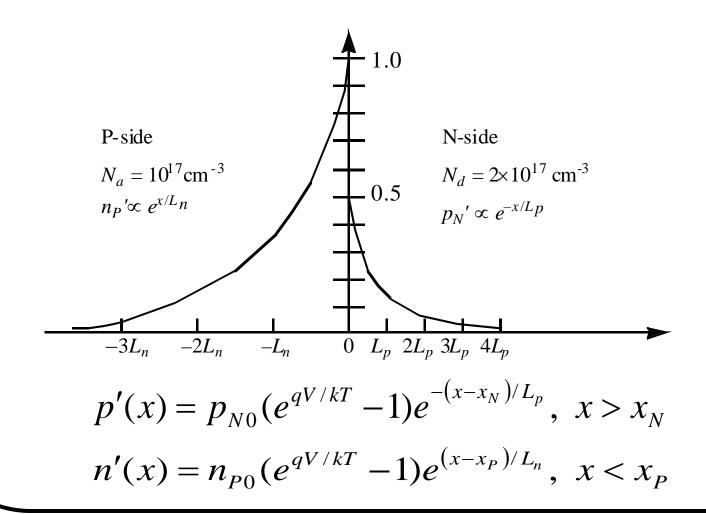

# 4.8 Forward Biased Junction-- Excess Carriers

$$\frac{d^2p'}{dx^2} = \frac{p'}{L_p^2}$$

$$p'(\infty) = 0$$

$$p'(x_N) = p_{N0}(e^{qV/kT} - 1)$$

$$p'(x) = Ae^{x/L_p} + Be^{-x/L_p}$$

$$p'(x) = p_{N0}(e^{qV/kT} - 1)e^{-(x-x_N)/L_p}, x > x_N$$

#### 4.8 Excess Carrier Distributions

#### EXAMPLE: Carrier Distribution in Forward-biased PN Diode

N-type

$$N_d = 5 \times 10^{17} \text{ cm}^{-3}$$

$D_p = 12 \text{ cm}^2/\text{s}$

$\tau_p = 1 \text{ } \mu\text{s}$

P-type

$$N_a = 10^{17} \text{ cm}^{-3}$$

$D_n = 36.4 \text{ cm}^2/\text{s}$

$\tau_n = 2 \text{ }\mu\text{s}$

• *Sketch* n'(x) *on the* P-*side*.

$$n'(x_P) = n_{P0}(e^{qV/kT} - 1) = \frac{n_i^2}{N_a}(e^{qV/kT} - 1) = \frac{10^{20}}{10^{17}}e^{0.6/0.026} = 10^{13} \text{ cm}^{-3}$$

#### EXAMPLE: Carrier Distribution in Forward-biased PN Diode

• How does  $L_n$  compare with a typical device size?

$$L_n = \sqrt{D_n \tau_n} = \sqrt{36 \times 2 \times 10^{-6}} = 85 \text{ } \mu\text{m}$$

• What is p'(x) on the P- side?

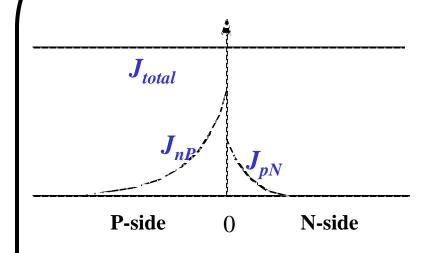

#### 4.9 PN Diode I-V Characteristics

= J at all x

$$J_{p} = J_{total} - J_{n}$$

$$J_{nP}$$

$$J_{pN}$$

P-side 0 N-side

$$J_{pN} = -qD_p \frac{dp'(x)}{dx} = q \frac{D_p}{L_p} p_{N0} (e^{qV/kT} - 1)e^{-(x-x_N)/L_p}$$

$$J_{nP} = qD_n \frac{dn'(x)}{dx} = q \frac{D_n}{L_n} n_{P0} (e^{qV/kT} - 1)e^{(x - x_P)/L_n}$$

Total current =

$$J_{pN}(x_N) + J_{nP}(x_P) = \left(q \frac{D_p}{L_p} p_{N0} + q \frac{D_n}{L_n} n_{P0}\right) (e^{qV/kT} - 1)$$

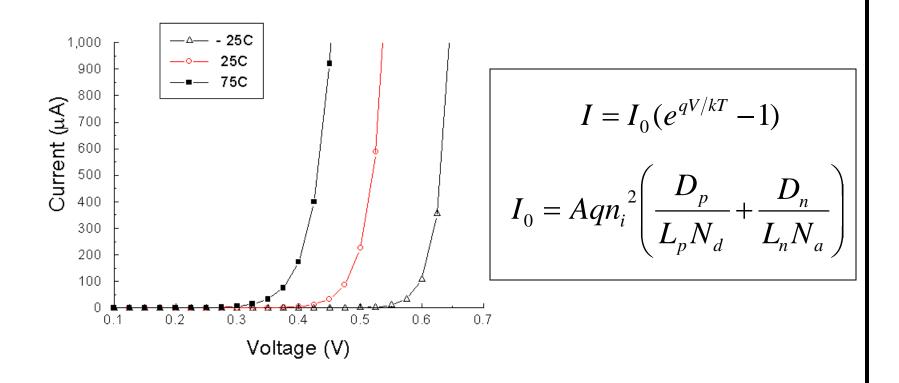

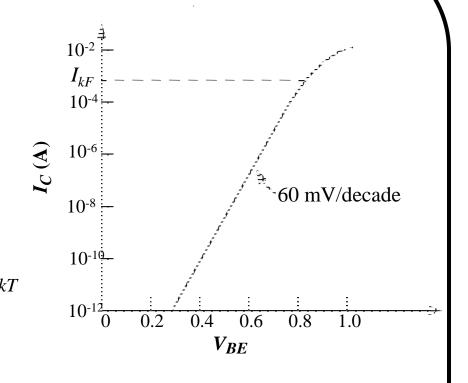

## The PN Junction as a Temperature Sensor

What causes the IV curves to shift to lower V at higher T?

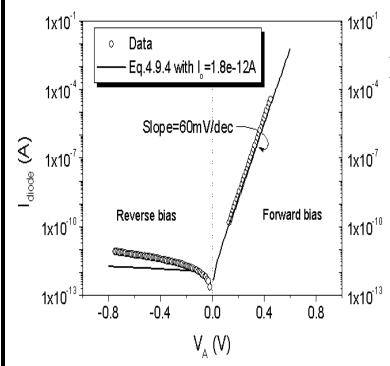

## 4.9.1 Contributions from the Depletion Region

$$I_{leakage} = I_0 + A \frac{q n_i W_{dep}}{\tau_{dep}}$$

$$n \approx p \approx n_i e^{qV/2kT}$$

Net recombination (generation) rate:

$$\frac{n_i}{\tau_{dep}}(e^{qV/2kT}-1)$$

$$I = I_0(e^{qV/kT} - 1) + A \frac{qn_iW_{dep}}{\tau_{dep}}(e^{qV/2kT} - 1)$$

**Space-Charge Region (SCR) current**

Under forward bias, SCR current is an extra current with a slope 120mV/decade

# 4.10 Charge Storage

What is the relationship between  $\tau_s$  (charge-storage time) and  $\tau$  (carrier lifetime)?

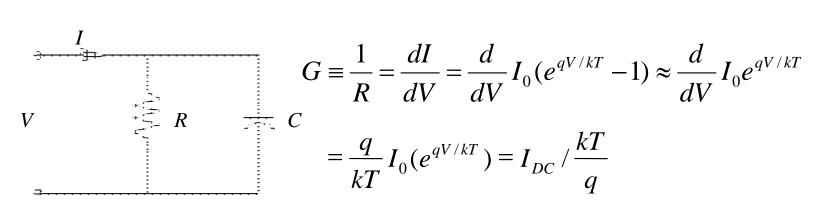

# 4.11 Small-signal Model of the Diode

What is G at 300K and  $I_{DC} = 1 \text{ mA}$ ?

## Diffusion Capacitance:

$$C = \frac{dQ}{dV} = \tau_s \frac{dI}{dV} = \tau_s G = \tau_s I_{DC} / \frac{kT}{q}$$

Which is larger, diffusion or depletion capacitance?

#### Part II: Application to Optoelectronic Devices

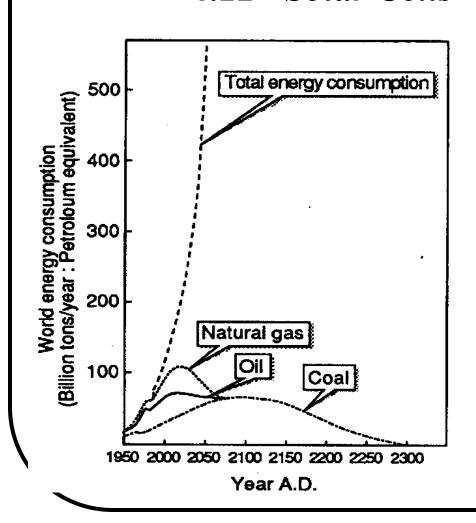

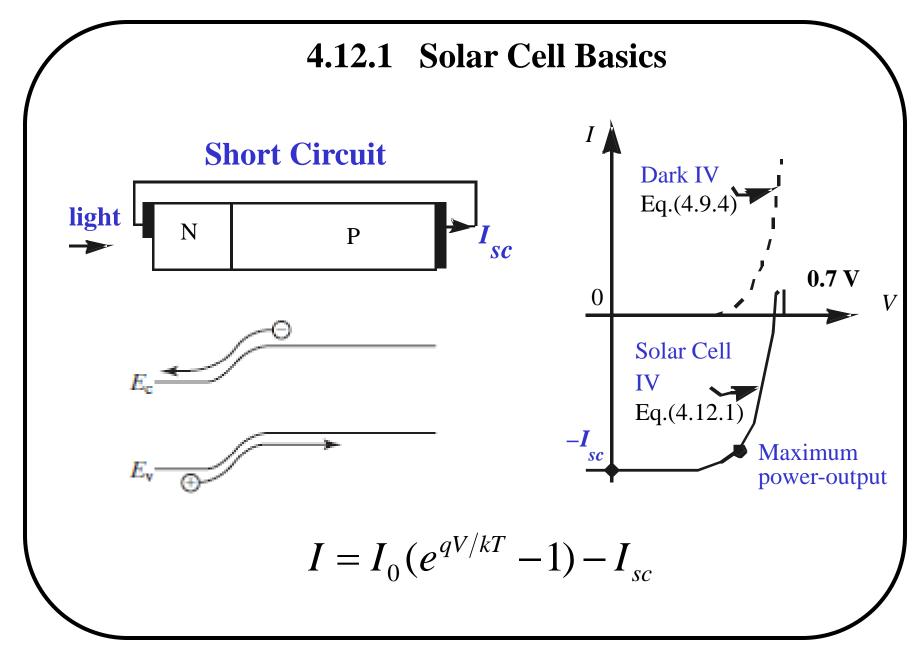

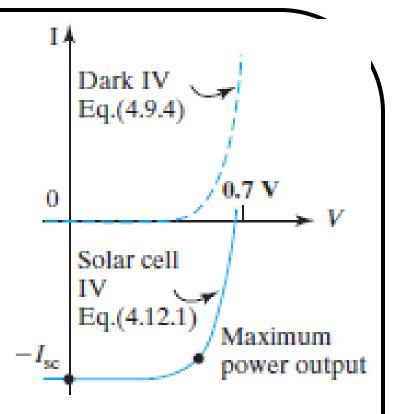

#### 4.12 Solar Cells

- •Solar Cells is also known as photovoltaic cells.

- •Converts sunlight to electricity with 10-30% conversion efficiency.

- •1 m<sup>2</sup> solar cell generate about 150 W peak or 25 W continuous power.

- •Low cost and high efficiency are needed for wide deployment.

# **Direct-Gap and Indirect-Gap Semiconductors**

- •Electrons have both particle and wave properties.

- •An electron has energy E and wave vector k.

direct-gap semiconductor

indirect-gap semiconductor

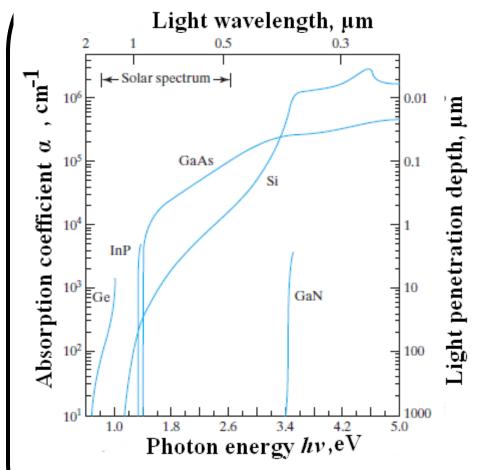

# 4.12.2 Light Absorption

Light intensity  $(x) \propto e^{-\alpha x}$

$\alpha(1/cm)$ : absorption coefficient

$1/\alpha$ : light penetration depth

Photon Energy (eV) =

$$\frac{hc}{\lambda}$$

=  $\frac{1.24}{\lambda} (\mu m)$

A thinner layer of direct-gap semiconductor can absorb most of solar radiation than indirect-gap semiconductor. But Si...

## 4.12.3 Short-Circuit Current and Open-Circuit Voltage

If light shines on the N-type semiconductor and generates holes (and electrons) at the rate of G s<sup>-1</sup>cm<sup>-3</sup>,

$$\frac{d^2p'}{dx^2} = \frac{p'}{L_p^2} - \frac{G}{D_p}$$

If the sample is uniform (no PN junction),  $d^2p'/dx^2 = 0 \implies p' = GL_p^2/D_p = G\tau_p$

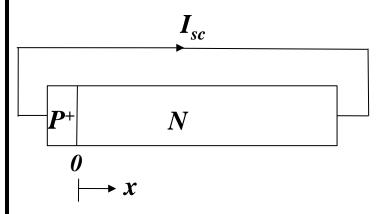

# Solar Cell Short-Circuit Current, I<sub>sc</sub>

Assume very thin P+ layer and carrier generation in N region only.

$$p'(\infty) = L_p^2 \frac{G}{D_p} = \tau_p G$$

$$p'(0) = 0$$

$$p'(x) = \tau_p G(1 - e^{-x/L_p})$$

$$T_pG$$

$T_pG$

$X$

$$J_{p} = -qD_{p} \frac{dp'(x)}{dx} = q \frac{D_{p}}{L_{p}} \tau_{p} G e^{-x/L_{p}}$$

$$I_{sc} = AJ_p(0) = AqL_pG$$

G is really not uniform.  $L_p$  needs be larger than the light penetration depth to collect most of the generated carriers.

#### Open-Circuit Voltage

•Total current is  $I_{SC}$  plus the PV diode (dark) current:

$$I = Aq \frac{n_i^2}{N_d} \frac{D_p}{L_p} (e^{qV/kT} - 1) - AqL_p G$$

•Solve for the open-circuit voltage ( $V_{oc}$ ) by setting I=0

(assuming  $e^{qV_{oc}/kT} >> 1$ )

$$0 = \frac{n_i^2}{N_d} \frac{D_p}{L_p} e^{qV_{oc}/kT} - L_p G$$

$$V_{oc} = \frac{kT}{q} \ln(\tau_p G N_d / n_i^2)$$

#### How to raise $V_{oc}$ ?

# 4.12.4 Output Power

A particular operating point on the solar cell I-V curve maximizes the output power (I ×V).

Output Power =

$$I_{sc} \times V_{oc} \times FF$$

•Si solar cell with 15-20% efficiency dominates the market now

- •Theoretically, the highest efficiency (~24%) can be obtained with 1.9eV >Eg>1.2eV. Larger Eg lead to too low Isc (low light absorption); smaller Eg leads to too low Voc.

- Tandem solar cells gets 35% efficiency using large and small Eg materials tailored to the short and long wavelength solar light.

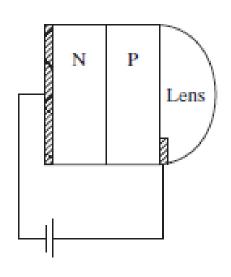

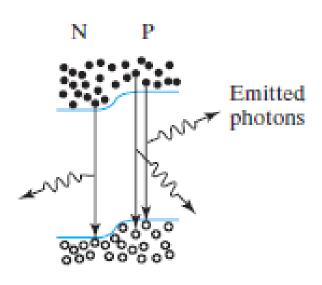

# 4.13 Light Emitting Diodes and Solid-State Lighting

#### Light emitting diodes (LEDs)

- LEDs are made of compound semiconductors such as InP and GaN.

- Light is emitted when electron and hole undergo *radiative recombination*.

# Direct and Indirect Band Gap

Direct band gap Example: GaAs

Direct recombination is efficient as k conservation is satisfied.

Indirect band gap Example: Si

Direct recombination is rare as k conservation is not satisfied

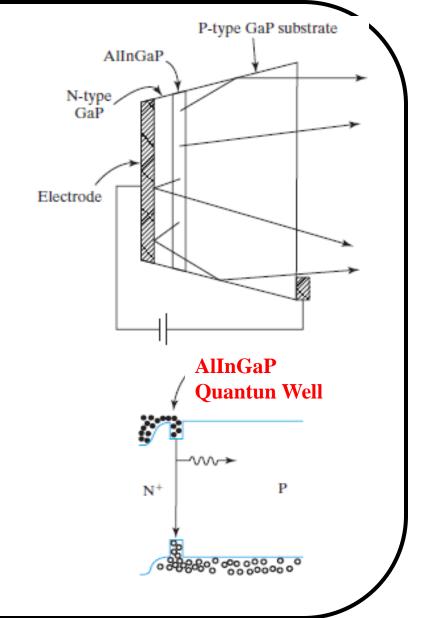

#### 4.13.1 LED Materials and Structure

LED wavelength (

$$\mu$$

m) =  $\frac{1.24}{\text{photon energy}} \approx \frac{1.24}{E_g(eV)}$

#### 4.13.1 LED Materials and Structure

|      | $E_g(eV)$ | Wavelength<br>(μm) | Color         | Lattice<br>constant<br>(Å) |

|------|-----------|--------------------|---------------|----------------------------|

| InAs | 0.36      | 3.44               |               | 6.05                       |

| InN  | 0.65      | 1.91               | infrared      | 3.45                       |

| InP  | 1.36      | 0.92               |               | 5.87                       |

| GaAs | 1.42      | 0.87               | Red<br>Yellow | 5.66                       |

| GaP  | 2.26      | 0.55               | Green<br>Blue | 5.46                       |

| AlP  | 3.39      | 0.51               |               | 5.45                       |

| GaN  | 2.45      | 0.37               | <b> </b>      | 3.19                       |

| AIN  | 6.20      | 0.20               | UV            | 3.11                       |

compound semiconductors

#### binary semiconductors:

- Ex: GaAs, efficient emitter

#### ternary semiconductor:

- Ex:  $GaAs_{1-x}P_x$ , tunable  $E_g$  (to vary the color)

#### quaternary semiconductors:

- Ex: AlInGaP, tunable  $E_g$  and lattice constant (for growing high quality epitaxial films on inexpensive substrates)

**Light-emitting diode materials**

#### **Common LEDs**

| Spectral range   | Material<br>System             | Substrate       | Example Applications                                               |  |

|------------------|--------------------------------|-----------------|--------------------------------------------------------------------|--|

| Infrared         | InGaAsP                        | InP             | Optical communication                                              |  |

| Infrared<br>-Red | GaAsP                          | GaAs            | Indicator lamps. Remote control                                    |  |

| Red-<br>Yellow   | AlInGaP                        | GaA or<br>GaP   | Optical communication.<br>High-brightness traffic<br>signal lights |  |

| Green-<br>Blue   | InGaN                          | GaN or sapphire | High brightness signal lights. Video billboards                    |  |

| Blue-UV          | AlInGaN                        | GaN or sapphire | Solid-state lighting                                               |  |

| Red-<br>Blue     | Organic<br>semicon-<br>ductors | glass           | Displays                                                           |  |

# 4.13.2 Solid-State Lighting

luminosity (lumen, lm): a measure of visible light energy normalized to the sensitivity of the human eye at different wavelengths

| Incandescent lamp | Compact<br>fluorescent<br>lamp | Tube<br>fluorescent<br>lamp | White<br>LED | Theoretical limit at peak of eye sensitivity ( λ=555nm) | Theoretical limit (white light) |

|-------------------|--------------------------------|-----------------------------|--------------|---------------------------------------------------------|---------------------------------|

| 17                | 60                             | 50-100                      | 90-?         | 683                                                     | ~340                            |

#### **Luminous efficacy of lamps in lumen/watt**

#### **Organic Light Emitting Diodes (OLED):**

has lower efficacy than nitride or aluminide based compound semiconductor LEDs.

Terms: luminosity measured in lumens. luminous efficacy,

# 4.14 Diode Lasers4.14.1 Light Amplification

(a) Absorption photon (b)

- (b) Spontaneous Emission

- (e) Net Light \( \mathcal{M} \rightarrow \quad \quad \mathcal{M} \rightarrow \quad \qq \quad \qu

(c) Stimulated

Emission photon

Light amplification requires population inversion: electron occupation probability is larger for higher E states than lower E states.

Stimulated emission: emitted photon has identical frequency and directionality as the stimulating photon; light wave is amplified.

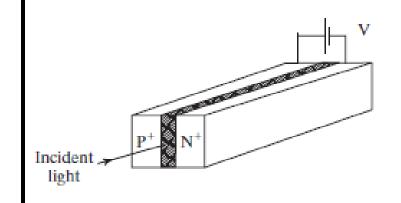

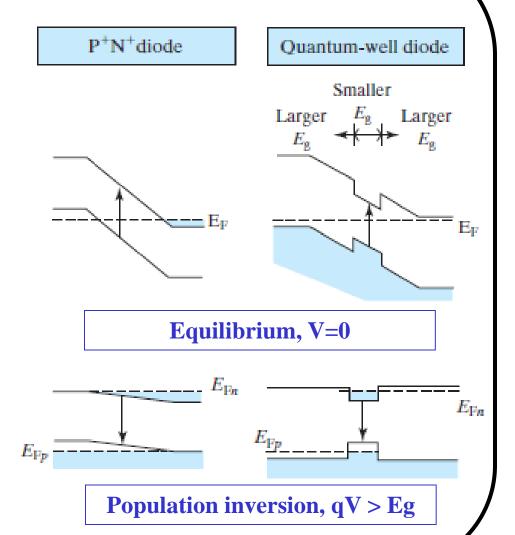

# 4.14.1 Light Amplification in PN Diode

Population inversion is achieved when

$$qV = E_{fn} - E_{fp} > E_g$$

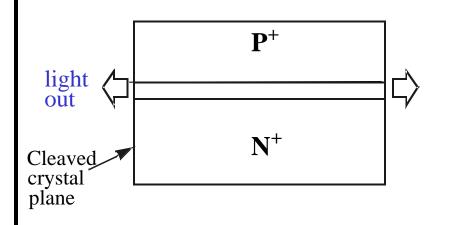

# 4.14.2 Optical Feedback and Laser

Laser threshold is reached (light intensity grows by feedback) when

$$R_1 \times R_2 \times G \ge 1$$

•R1, R2: reflectivities of the two ends

•G: light amplification factor (gain) for a round-trip travel of the light through the diode

Light intensity grows until  $R_1 \times R_2 \times G = 1$ , when the light intensity is just large enough to stimulate carrier recombinations at the same rate the carriers are injected by the diode current.

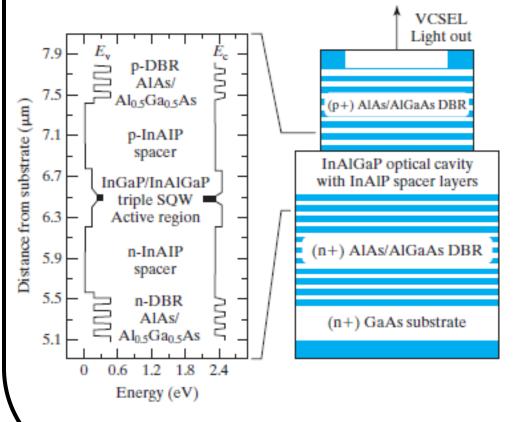

#### 4.14.2 Optical Feedback and Laser Diode

- Distributed Bragg reflector (DBR) reflects light with multi-layers of semiconductors.

- •Vertical-cavity surfaceemitting laser (VCSEL) is shown on the left.

- •Quantum-well laser has smaller threshold current because fewer carriers are needed to achieve population inversion in the small volume of the thin small-*Eg* well.

## 4.14.3 Laser Applications

**Red diode lasers**: CD, DVD reader/writer

Blue diode lasers: Blu-ray DVD (higher storage density)

1.55 µm infrared diode lasers: Fiber-optic communication

#### 4.15 Photodiodes

**Photodiodes:** Reverse biased PN diode. Detects photogenerated current (similar to Isc of solar cell) for optical communication, DVD reader, etc.

Avalanche photodiodes: Photodiodes operating near avalanche breakdown amplifies photocurrent by impact ionization.

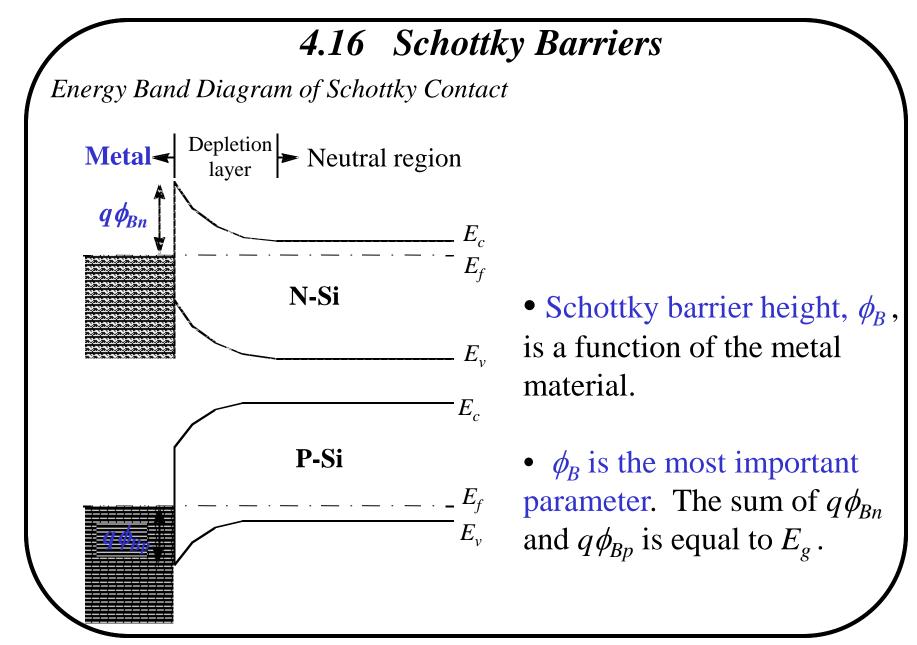

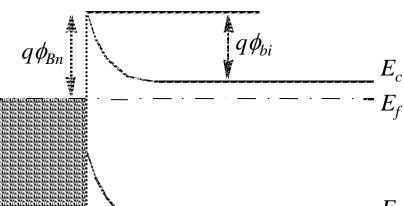

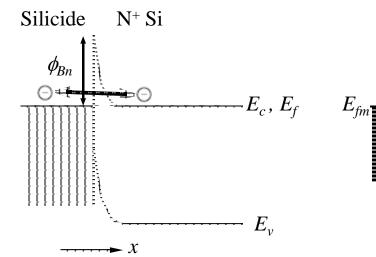

# Part III: Metal-Semiconductor Junction

Two kinds of metal-semiconductor contacts:

- Rectifying Schottky diodes: metal on lightly doped silicon

- •Low-resistance ohmic contacts: metal on heavily doped silicon

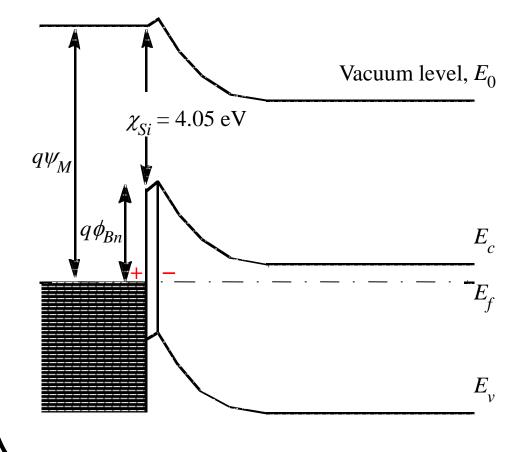

# $\phi_{Rn}$ Increases with Increasing Metal Work Function Vacuum level, $E_0$ $\chi_{Si} = 4.05 \text{ eV}$ $\Psi_M$ : Work Function of metal $q\psi_{M}$ $\chi_{Si}$ : Electron Affinity of Si $E_c$ $E_f$ Theoretically, $\phi_{Bn} = \psi_M - \chi_{Si}$ $E_{\nu}$

#### Schottky barrier heights for electrons and holes

| Metal           | Mg  | Ti   | Cr   | W    | Mo   | Pd   | Au  | Pt  |

|-----------------|-----|------|------|------|------|------|-----|-----|

| $\phi_{Bn}$ (V) | 0.4 | 0.5  | 0.61 | 0.67 | 0.68 | 0.77 | 0.8 | 0.9 |

| $\phi_{Bp}(V)$  |     | 0.61 | 0.5  |      | 0.42 |      | 0.3 |     |

| Work            |     |      |      |      |      |      |     |     |

| Function        | 3.7 | 4.3  | 4.5  | 4.6  | 4.6  | 5.1  | 5.1 | 5.7 |

| $\psi_m(V)$     |     |      |      |      |      |      |     |     |

$$\phi_{Bn} + \phi_{Bp} \approx E_g$$

$\phi_{Bn}$  increases with increasing metal work function

# Fermi Level Pinning

- A high density of energy states in the bandgap at the metalsemiconductor interface pins  $E_f$  to a narrow range and  $\phi_{Bn}$  is typically 0.4 to 0.9 V

- *Question*: What is the typical range of  $\phi_{Bp}$ ?

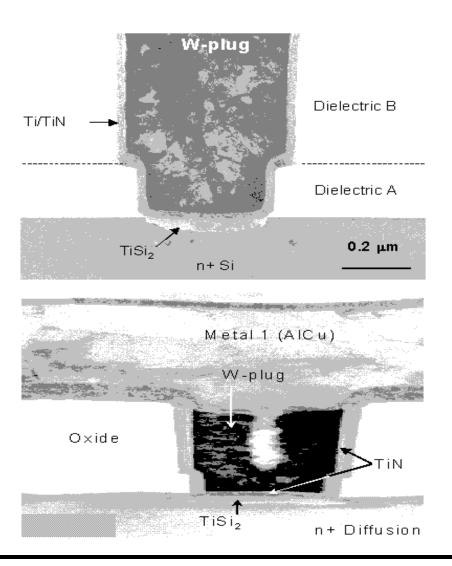

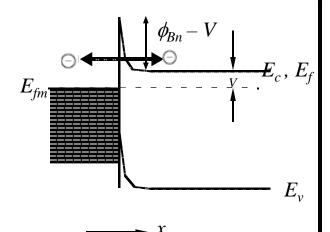

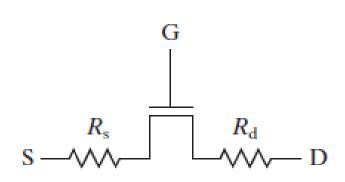

#### Schottky Contacts of Metal Silicide on Si

**Silicide:** A silicon and metal compound. It is conductive similar to a metal.

Silicide-Si interfaces are more stable than metal-silicon interfaces. After metal is deposited on Si, an annealing step is applied to form a silicide-Si contact. The term *metal-silicon contact* includes and almost always means silicide-Si contacts.

| Silicide       | ErSi <sub>1.7</sub> | HfSi | MoSi <sub>2</sub> | ZrSi <sub>2</sub> | TiSi <sub>2</sub> | CoSi <sub>2</sub> | WSi <sub>2</sub> | NiSi <sub>2</sub> | Pd <sub>2</sub> Si | PtSi |

|----------------|---------------------|------|-------------------|-------------------|-------------------|-------------------|------------------|-------------------|--------------------|------|

| $\phi_{Bn}(V)$ | 0.28                | 0.45 | 0.55              | 0.55              | 0.61              | 0.65              | 0.67             | 0.67              | 0.75               | 0.87 |

| $\phi_{Bp}(V)$ |                     |      | 0.55              | 0.49              | 0.45              | 0.45              | 0.43             | 0.43              | 0.35               | 0.23 |

# Using C-V Data to Determine $\phi_B$

$$q\phi_{bi} = q\phi_{Bn} - (E_c - E_f)$$

$$= q\phi_{Bn} - kT \ln \frac{N_c}{N_d}$$

$$W_{dep} = \sqrt{\frac{2\varepsilon_s(\phi_{bi} + V)}{qN_d}}$$

$$C = \frac{\varepsilon_s}{W_{dep}} A$$

#### Question:

How should we plot the CV  $E_v$  data to extract  $\phi_{bi}$ ?

# Using CV Data to Determine $\phi_B$

Once  $\phi_{bi}$  is known,  $\phi_B$  can be determined using

$$q\phi_{bi} = q\phi_{Bn} - (E_c - E_f) = q\phi_{Bn} - kT \ln \frac{N_c}{N_d}$$

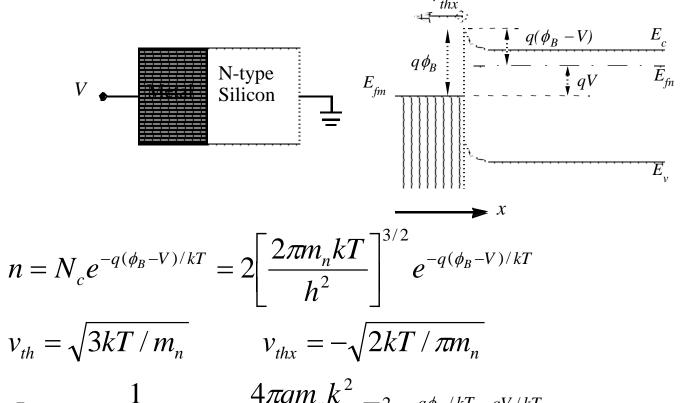

# 4.17 Thermionic Emission Theory

$$J_{S \to M} = -\frac{1}{2} qn v_{thx} = \frac{4\pi q m_n k^2}{h^3} T^2 e^{-q\phi_B/kT} e^{qV/kT}$$

=  $J_0 e^{qV/kT}$ , where  $J_o \approx 100 e^{-q\phi_B/kT}$  A/cm<sup>2</sup>

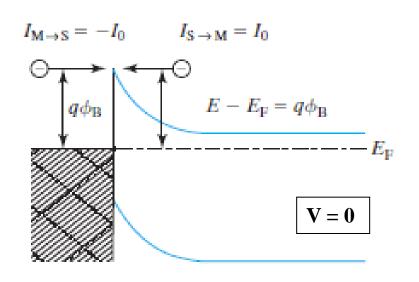

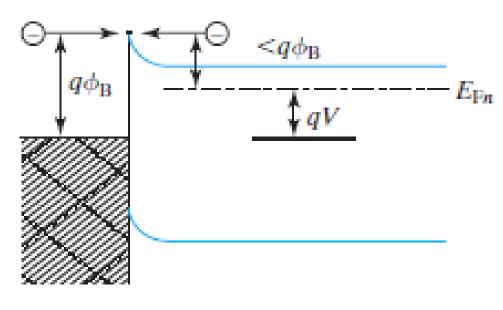

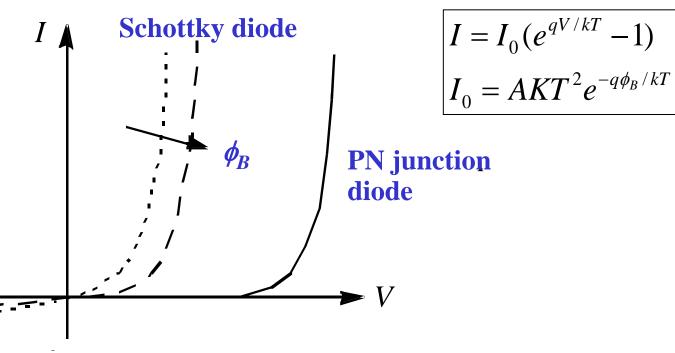

# 4.18 Schottky Diodes

# 4.18 Schottky Diodes

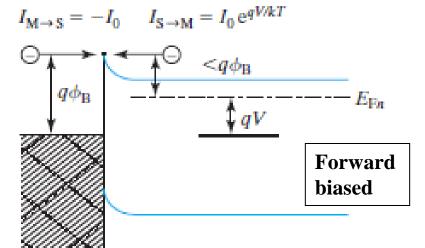

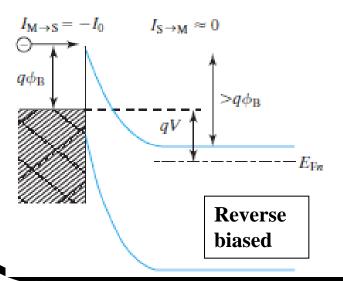

$$I_{M\rightarrow S} = -I_0$$

$I_{S\rightarrow M} = I_0 e^{qV/kT}$

$$I_0 = AKT^2 e^{-q\phi_B/kT}$$

$$K = \frac{4\pi q m_n k^2}{h^3} \approx 100 \text{ A/(cm}^2 \cdot \text{K}^2)$$

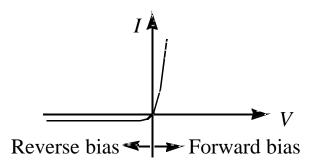

$$I = I_{S \to M} + I_{M \to S} = I_0 e^{qV/kT} - I_0 = I_0 (e^{qV/kT} - 1)$$

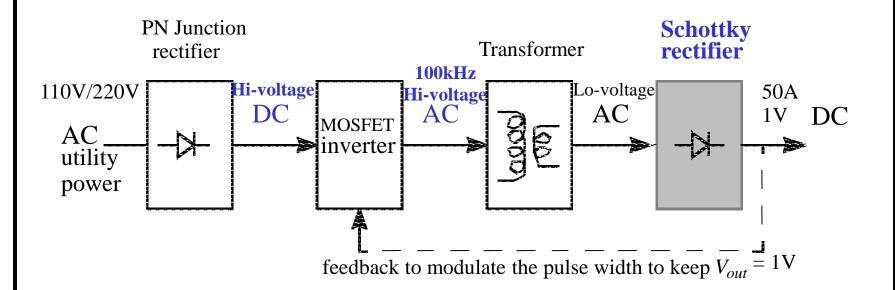

# 4.19 Applications of Schottly Diodes

- $I_0$  of a Schottky diode is  $10^3$  to  $10^8$  times larger than a PN junction diode, depending on  $\phi_B$ . A larger  $I_0$  means a smaller forward drop V.

- A Schottky diode is the preferred rectifier in low voltage, high current applications.

# Switching Power Supply

# 4.19 Applications of Schottky diodes

**Question:** What sets the lower limit in a Schottky diode's forward drop?

- *Synchronous Rectifier*: For an even lower forward drop, replace the diode with a wide-W MOSFET which is not bound by the tradeoff between diode *V* and leakage current.

- There is no minority carrier injection at the Schottky junction. Therefore, Schottky diodes can operate at higher frequencies than PN junction diodes.

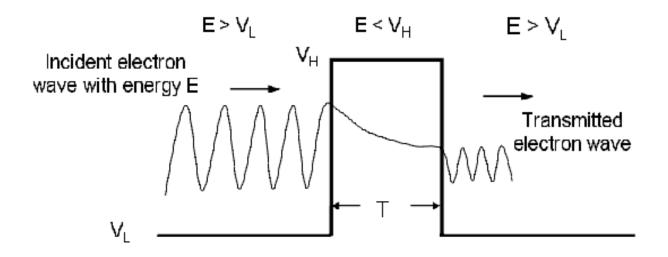

# 4.20 Quantum Mechanical Tunneling

#### Tunneling probability:

$$P \approx \exp\left(-2T\sqrt{\frac{8\pi^2 m}{h^2}(V_H - E)}\right)$$

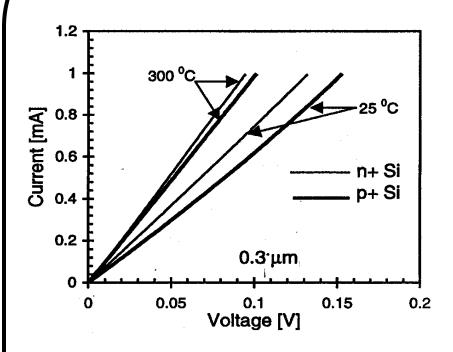

#### 4.21 Ohmic Contacts

#### 4.21 Ohmic Contacts

$$W_{dep} = \sqrt{\frac{2\varepsilon_s \phi_{Bn}}{qN_d}}$$

Tunneling probability:

$$P pprox e^{-H\phi_{Bn}/\sqrt{N_d}}$$

$$T \approx W_{dep} / 2 = \sqrt{\varepsilon_s \phi_{Bn} / 2qN_d}$$

$$H = \frac{4\pi}{h} \sqrt{\varepsilon_s m_n / q}$$

$$J_{S \to M} \approx \frac{1}{2} q N_d v_{thx} P = q N_d \sqrt{kT / 2\pi m_n} e^{-H(\phi_{Bn} - V) / \sqrt{N_d}}$$

#### 4.21 Ohmic Contacts

$$R_c \equiv \left(\frac{dJ_{S \to M}}{dV}\right)^{-1} = \frac{2e^{H\phi_{Bn}/\sqrt{N_d}}}{qv_{thx}H\sqrt{N_d}} \propto e^{H\phi_{Bn}/\sqrt{N_d}} \Omega \cdot \text{cm}^2$$

#### Part I: PN Junction

$$\phi_{bi} = \frac{kT}{q} \ln \frac{N_d N_a}{n_i^2}$$

The potential barrier increases by 1 V if a 1 V reverse bias is applied

depletion width

$$W_{dep} = \sqrt{\frac{2\varepsilon_{s} \cdot potential \ barrier}{qN}}$$

junction capacitance

$$C_{dep} = A \frac{\mathcal{E}_s}{W_{dep}}$$

- Under forward bias, minority carriers are injected across the jucntion.

- The quasi-equilibrium boundary condition of minority carrier densities is:

$$n(x_p) = n_{P0}e^{qV/kT}$$

$$p(x_N) = p_{N0}e^{qV/kT}$$

• Most of the minority carriers are injected into the more lightly doped side.

• Steady-state continuity equation:

$$\frac{d^2p'}{dx^2} = \frac{p'}{D_p\tau_p} = \frac{p'}{L_p^2}$$

$$L_p \equiv \sqrt{D_p \tau_p}$$

- Minority carriers diffuse outward  $\propto e^{-|x|/L_p}$  and  $e^{-|x|/L_n}$

- $L_p$  and  $L_n$  are the diffusion lengths

$$I = I_0(e^{qV/kT} - 1)$$

$$I_0 = Aqn_i^2 \left( \frac{D_p}{L_p N_d} + \frac{D_n}{L_n N_a} \right)$$

Charge storage:

$$Q = I\tau_s$$

Diffusion capacitance:

$$C = \tau_s G$$

Diode conductance:

$$G = I_{DC} / \frac{kT}{q}$$

## Part II: Optoelectronic Applications

Solar cell power =  $I_{sc} \times V_{oc} \times FF$

- •~100um Si or <1um direct—gap semiconductor can absorb most of solar photons with energy larger than  $E_g$ .

- •Carriers generated within diffusion length from the junction can be collected and contribute to the Short Circuit Current  $I_{sc}$ .

- •Theoretically, the highest efficiency (~24%) can be obtained with 1.9eV > $E_g$ >1.2eV. Larger  $E_g$  lead to too low  $I_{sc}$  (low light absorption); smaller  $E_g$  leads to too low Open Circuit VoltageVoc.

- •Si cells with ~15% efficiency dominate the market. >2x cost reduction (including package and installation) is required to achieve cost parity with base-load non-renewable electricity.

#### LED and Solid-State Lighting

- •Electron-hole recombination in direct-gap semiconductors such as GaAs produce light.

- •Tenary semiconductors such as GaAsP provide tunable  $E_g$  and LED color.

- •Quaternary semiconductors such as AlInGaP provide tunable  $E_g$  and lattice constants for high quality epitaxial growth on inexpensive substrates.

- •Beyond displays, communication, and traffic lights, a new application is space lighting with luminous efficacy >5x higher than incandescent lamps. White light can be obtained with UV LED and phosphors. Cost still an issue.

- •Organic semiconductor is an important low-cost LED material class.

#### Laser Diodes

- •Light is amplified under the condition of population inversion states at higher E have higher probability of occupation than states at lower E.

- ullet Population inversion occurs when diode forward bias  $qV > E_g$ .

- •Optical feedback is provided with cleaved surfaces or distributed Bragg reflectors.

- •When the round-trip gain (including loss at reflector) exceeds unity, laser threshold is reached.

- •Quantum-well structures significantly reduce the threshold currents.

- •Purity of laser light frequency enables long-distance fiber-optic communication. Purity of light direction allows focusing to tiny spots and enables DVD writer/reader and other application.

#### Part III: Metal-Semiconductor Junction

$$I_0 = AKT^2 e^{-q\phi_B/kT}$$

- •Schottky diodes have large reverse saturation current, determined by the Schottky barrier height  $\phi_B$ , and therefore lower forward voltage at a given current density.

- •Ohmic contacts relies on tunneling. Low resistance contact requires low  $\phi_B$  and higher doping concentration.

$$R_c \propto e^{-(\frac{4\pi}{h}\phi_B\sqrt{\varepsilon_s m_n/qN_d})} \Omega \cdot \text{cm}^2$$

# $\phi_{Bn}$ Increases with Increasing Metal Work Function Vacuum level, $E_0$ = 4.05 eVIdeally, $q\psi_{M}$ $\phi_{Bn} = \psi_M - \chi_{Si}$ $E_c$ $E_{v}$

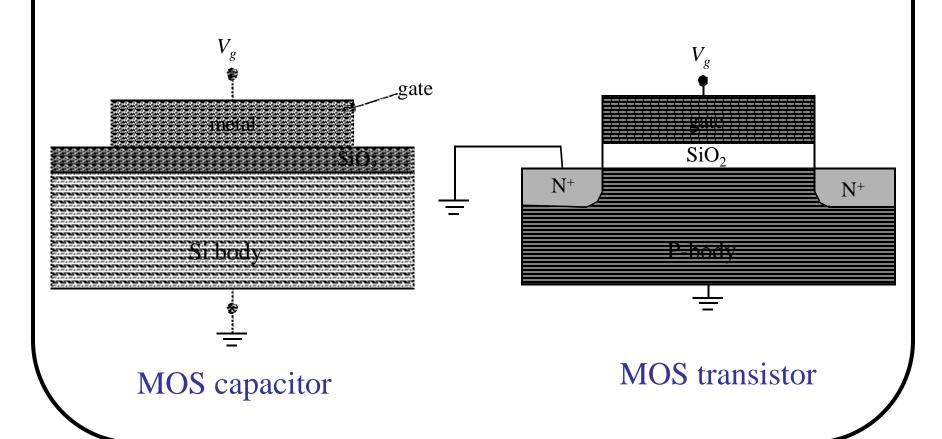

# Chapter 5 MOS Capacitor

MOS: Metal-Oxide-Semiconductor

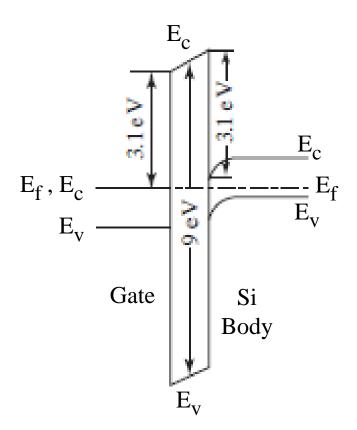

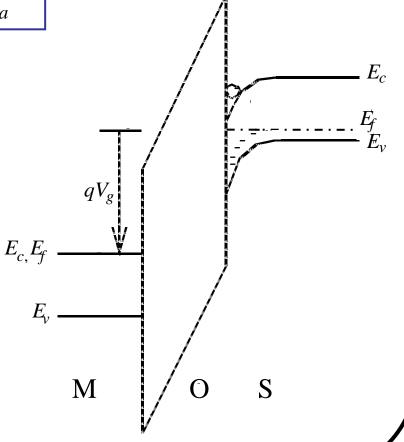

# Chapter 5 MOS Capacitor

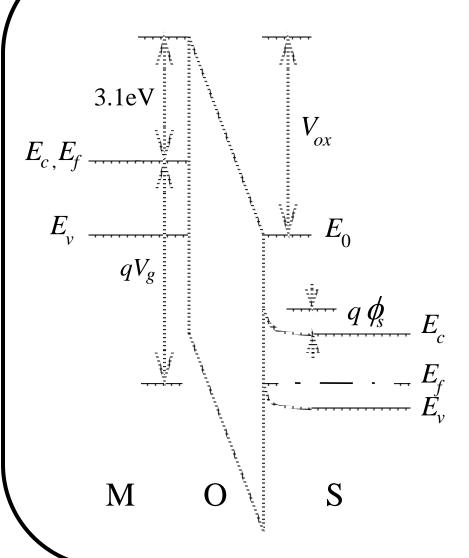

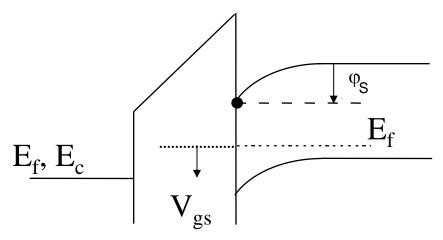

This energy-band diagram for  $V_g = 0$  is not the simplest one.

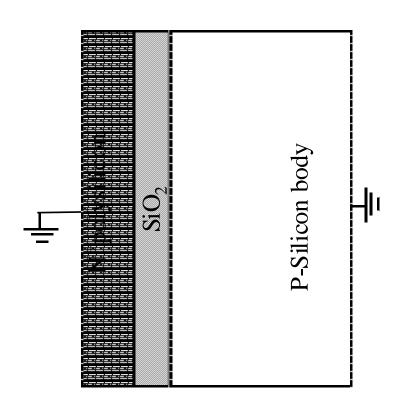

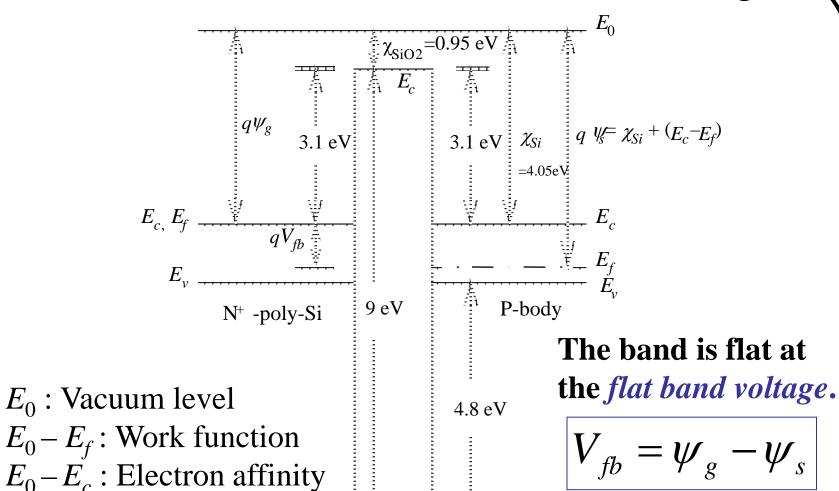

#### 5.1 Flat-band Condition and Flat-band Voltage

SiO<sub>2</sub>

Si/SiO<sub>2</sub> energy barrier

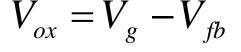

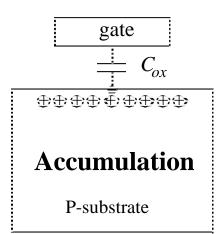

## 5.2 Surface Accumulation

Make

$$V_g < V_{fb}$$

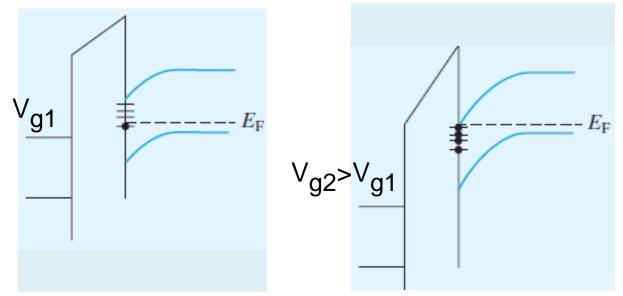

$$V_g = V_{fb} + \phi_s + V_{ox}$$

$\phi_s$ : surface potential, band bending

$V_{ox}$ : voltage across the oxide

$\phi_s$  is negligible when the surface is in accumulation.

## 5.2 Surface Accumulation

Gauss's Law

$$\rightarrow V_{ox} = -Q_{acc} / C_{ox}$$

$$Q_{acc} = -C_{ox}(V_g - V_{fb})$$

$$V_{ox} = -Q_s / C_{ox}$$

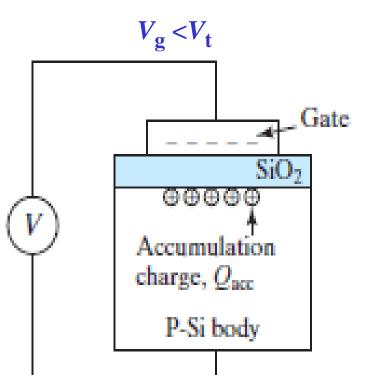

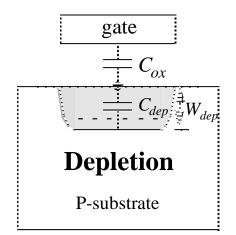

# 5.3 Surface Depletion $(V_g > V_{fb})$

$$qV_{ox}$$

$qV_{ox}$

$E_c$

$qV_g$

$E_c, E_f$

$W_{dep}$

$E_v$

$E_v$

$$V_{ox} = -\frac{Q_s}{C_{ox}} = -\frac{Q_{dep}}{C_{ox}} = \frac{qN_aW_{dep}}{C_{ox}} = \frac{\sqrt{qN_a 2\varepsilon_s \phi}}{C_{ox}}$$

### 5.3 Surface Depletion

$$V_{g} = V_{fb} + \phi_{s} + V_{ox} = V_{fb} + \phi_{s} + \frac{\sqrt{qN_{a}2\varepsilon_{s}\phi_{s}}}{C_{ox}}$$

This equation can be solved to yield  $\phi_s$ .

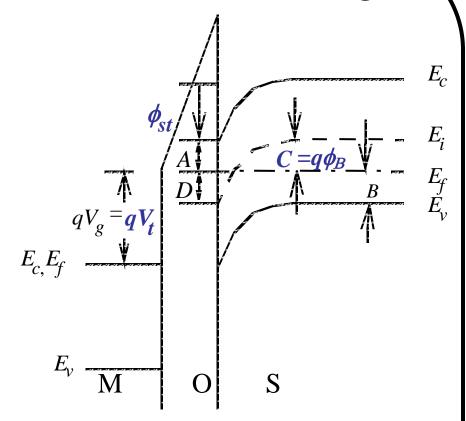

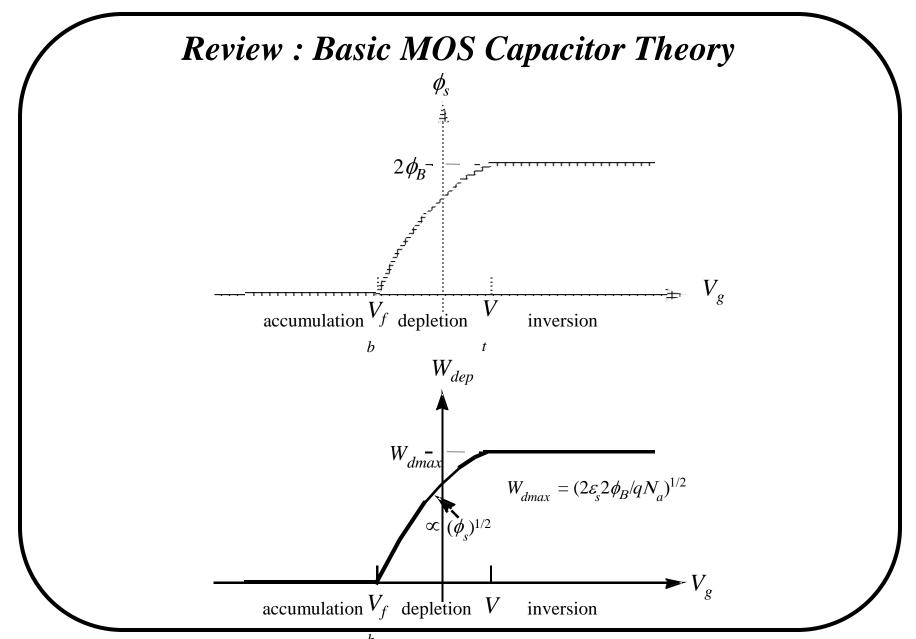

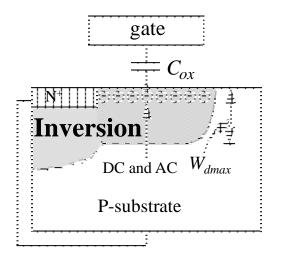

#### 5.4 Threshold Condition and Threshold Voltage

#### Threshold (of inversion):

$$n_s = N_a$$

, or

$$(E_c-E_f)_{surface} = (E_f-E_v)_{bulk}$$

, or

$$A=B$$

, and  $C=D$

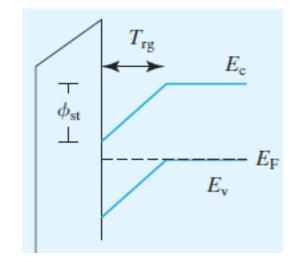

$$\phi_{st} = 2\phi_B = 2\frac{kT}{q} \ln\left(\frac{N_a}{n_i}\right)$$

$$q\phi_B = \frac{E_g}{2} - (E_f - E_v)|_{bulk} = \frac{kT}{q} \ln\left(\frac{N_v}{n_i}\right) - \frac{kT}{q} \ln\left(\frac{N_v}{N_a}\right) = \frac{kT}{q} \ln\left(\frac{N_a}{n_i}\right)$$

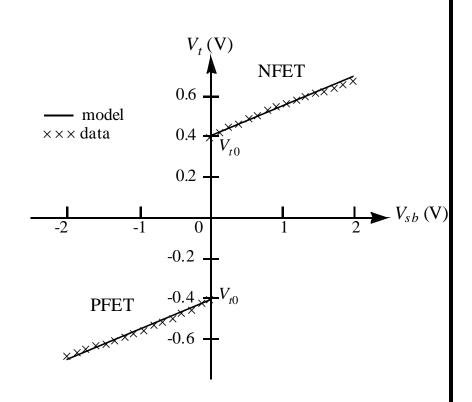

#### Threshold Voltage

$$V_g = V_{fb} + \varphi_s + V_{ox}$$

At threshold,

$$\varphi_{st} = 2\phi_B = 2\frac{kT}{q} \ln\left(\frac{N_a}{n_i}\right)$$

$$V_{ox} = \frac{\sqrt{qN_a 2\varepsilon_s 2\phi_B}}{C_{ox}}$$

$$V_{t} = V_{g}$$

at threshold  $= V_{fb} + 2\phi_{B} + \frac{\sqrt{qN_{a}2\varepsilon_{s}2\phi_{B}}}{C_{ox}}$

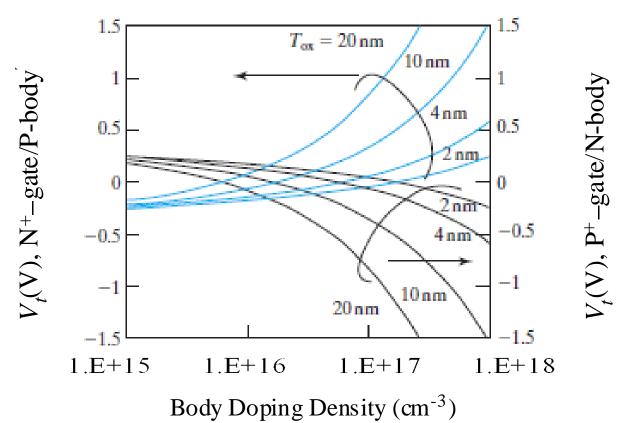

$$V_{t} = V_{fb} \pm 2\phi_{B} \pm \frac{\sqrt{qN_{sub} 2\varepsilon_{s} 2\phi_{B}}}{C_{ox}}$$

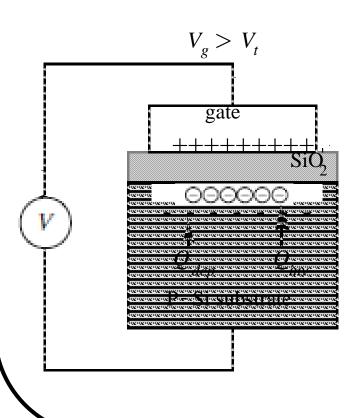

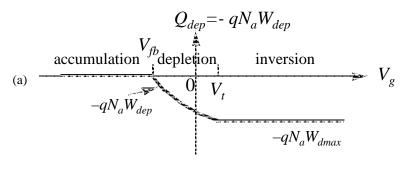

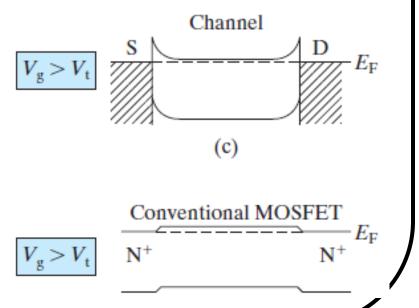

## 5.5 Strong Inversion-Beyond Threshold

$$V_g > V_i$$

$$W_{dep} = W_{dmax} = \sqrt{\frac{2\varepsilon_s 2\phi_B}{qN_a}}$$

## Inversion Layer Charge, $Q_{inv}$ (C/cm<sup>2</sup>)

$$V_{g} = V_{fb} + 2\phi_{B} - \frac{Q_{dep}}{C_{ox}} - \frac{Q_{inv}}{C_{ox}} = V_{fb} + 2\phi_{B} + \frac{\sqrt{qN_{a}2\varepsilon_{s}2\phi_{B}}}{C_{ox}} - \frac{Q_{inv}}{C_{ox}}$$

$$= V_{t} - \frac{Q_{inv}}{C_{ox}} \qquad \therefore \qquad Q_{inv} = -C_{ox}(V_{g} - V_{t})$$

$$V_{g} > V_{t}$$

## 5.5.1 Choice of $V_t$ and Gate Doping Type

$V_t$  is generally set at a small positive value so that, at  $V_g = 0$ , the transistor does not have an inversion layer and current does not flow between the two  $N^+$  regions

- P-body is normally paired with  $N^+$ -gate to achieve a small positive threshold voltage.

- N-body is normally paired with P+-gate to achieve a small negative threshold voltage.

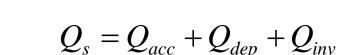

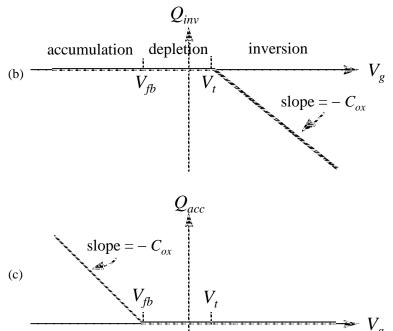

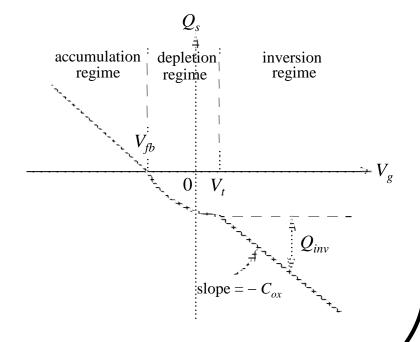

#### Review: Basic MOS Capacitor Theory

total substrate charge,  $Q_s$

inversion

accumulation depletion

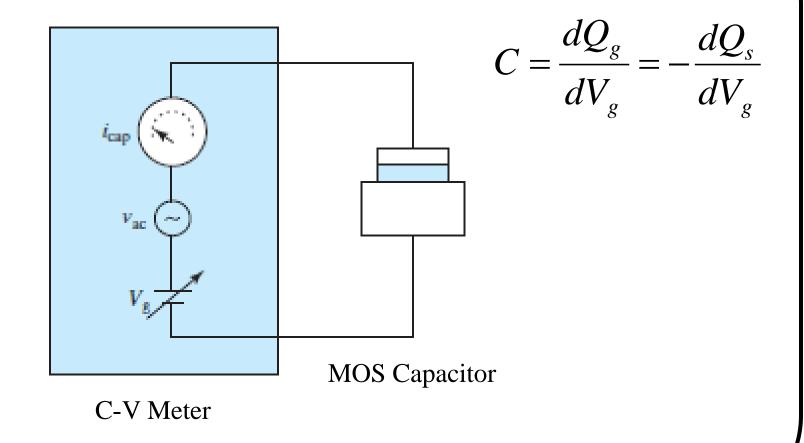

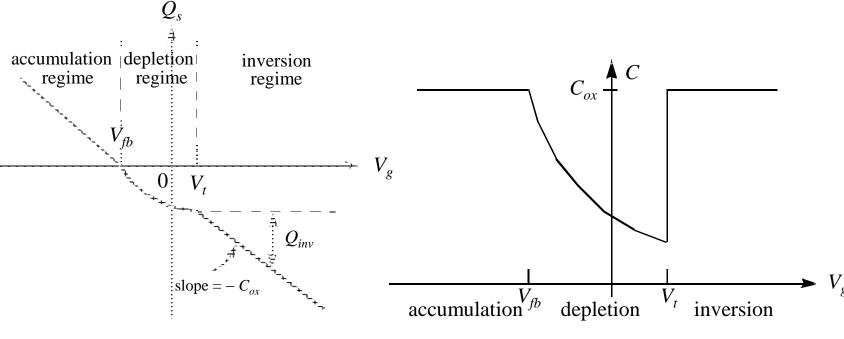

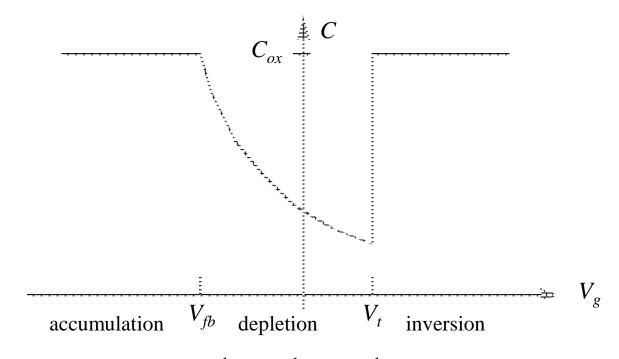

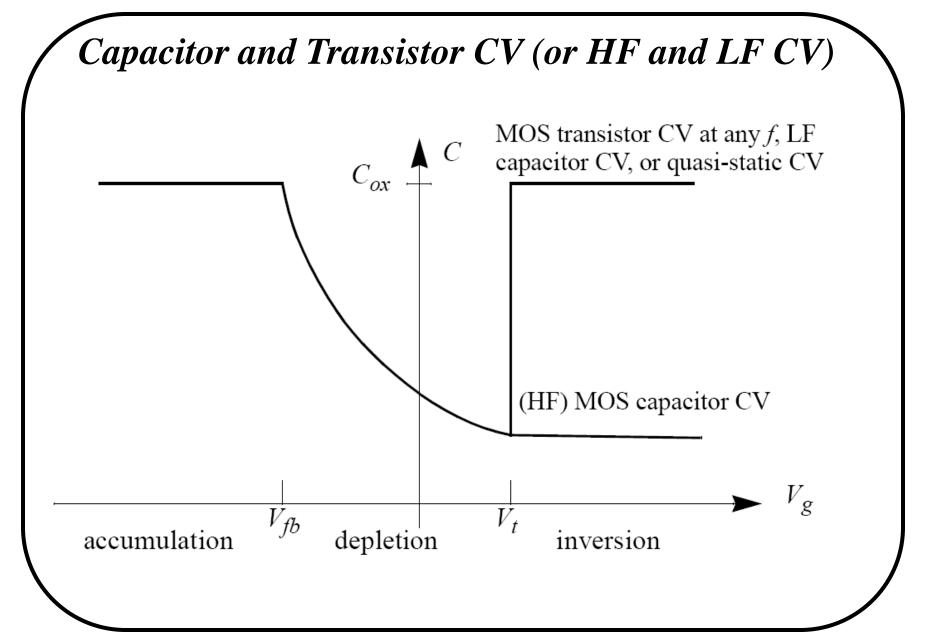

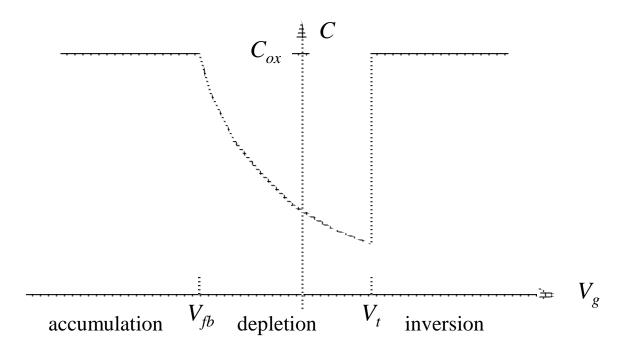

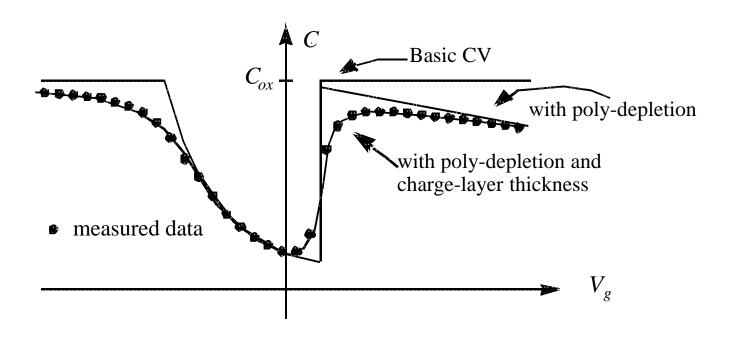

#### 5.6 MOS CV Characteristics

#### 5.6 MOS CV Characteristics

$$C = \frac{dQ_g}{dV_g} = -\frac{dQ_s}{dV_g}$$

#### CV Characteristics

In the depletion regime:

$$\frac{1}{C} = \frac{1}{C_{ox}} + \frac{1}{C_{dep}}$$

$$\frac{1}{C} = \sqrt{\frac{1}{C_{ox}^2} + \frac{2(V_g - V_{fb})}{qN_a \varepsilon_s}}$$

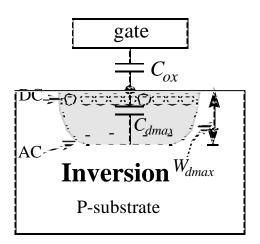

#### Supply of Inversion Charge May be Limited

In each case, C = ?

## Quasi-Static CV of MOS Capacitor

The quasi-static CV is obtained by the application of a slow linear-ramp voltage (< 0.1 V/s) to the gate, while measuring  $I_g$  with a very sensitive DC ammeter. C is calculated from  $I_g = C \cdot dV_g/dt$ . This allows sufficient time for  $Q_{inv}$  to respond to the slow-changing  $V_g$ .

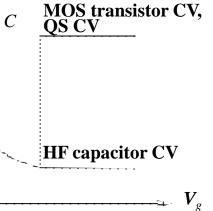

#### EXAMPLE: CV of MOS Capacitor and Transistor

Does the QS CV or the HF capacitor CV apply?

(1) MOS transistor, 10kHz. (Answer: QS CV).

(2) MOS transistor, 100MHz. (Answer: QS CV).

(3) MOS capacitor, 100MHz. (Answer: HF capacitor CV).

(4) MOS capacitor, 10kHz. (Answer: HF capacitor CV).

(5) MOS capacitor, slow  $V_g$  ramp. (Answer: QS CV).

(6) MOS transistor, slow  $V_g$  ramp. (Answer: QS CV).

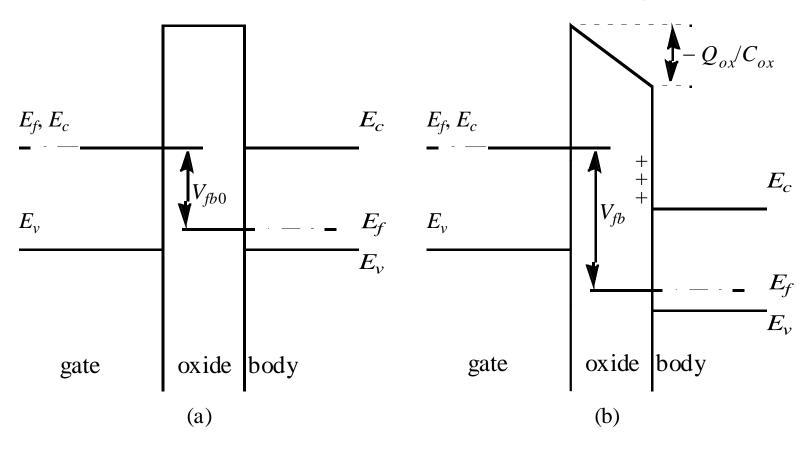

# 5.7 Oxide Charge-A Modification to $V_{fb}$ and $V_t$

$$V_{fb} = V_{fb0} - Q_{ox} / C_{ox} = \psi_g - \psi_s - Q_{ox} / C_{ox}$$

# 5.7 Oxide Charge-A Modification to $V_{fb}$ and $V_t$

#### Types of oxide charge:

- Fixed oxide charge, Si<sup>+</sup>

- Mobile oxide charge, due to Na<sup>+</sup>contamination

- Interface traps, neutral or charged depending on Vg.

- Voltage/temperature stress induced charge and traps--a reliability issue

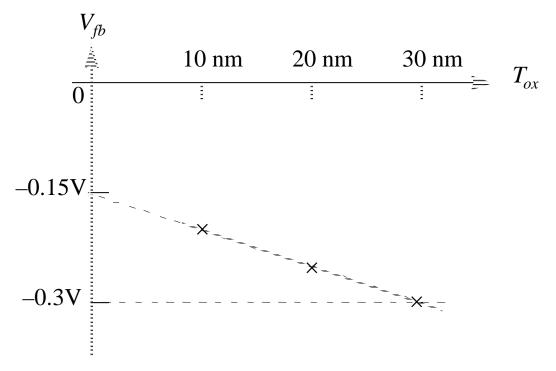

**EXAMPLE:** Interpret this measured  $V_{fb}$  dependence on oxide thickness. The gate electrode is  $N^+$  poly-silicon.

What does it tell us? Body work function? Doping type? Other?

Solution:

$$V_{fb} = \psi_g - \psi_s - Q_{ox}T_{ox} / \varepsilon_{ox}$$

## from intercept $\rightarrow \psi_g - \psi_s = -0.15 \text{ V}$

$$E_{f}, E_{c} = \psi_{g} + 0.15 V$$

$$E_{f}, E_{c} = E_{c}$$

$$E_{f}$$

$$E_{v}$$

\_\_\_\_\_  $E_{v}$  \_\_\_\_\_  $E_{v}$  \_\_\_\_\_ Si body

N-type substrate,

$$N_d = n = N_c e^{-0.15 \text{ eV/kT}} \approx 10^{17} \text{ cm}^{-3}$$

from slope  $\longrightarrow Q_{ox} = 1.7 \times 10^{-8} \text{ C/cm}^2$

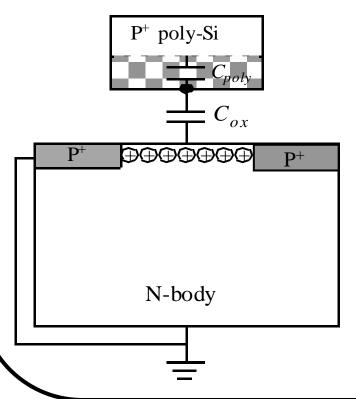

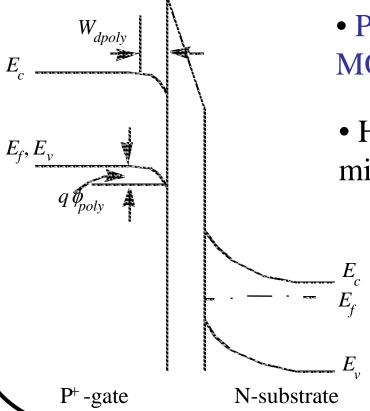

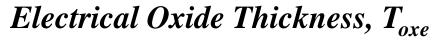

# 5.8 Poly-Silicon Gate Depletion–Effective Increase in $T_{ox}$

Gauss's Law

$$W_{dpoly} = \varepsilon_{ox} \mathbf{E}_{ox} / qN_{poly}$$

$$C = \left(\frac{1}{C_{ox}} + \frac{1}{C_{poly}}\right)^{-1} = \left(\frac{T_{ox}}{\varepsilon_{ox}} + \frac{W_{dpoly}}{\varepsilon_{s}}\right)^{-1}$$

$$= \frac{\varepsilon_{ox}}{T_{ox} + W_{dpoly} / 3}$$

If  $W_{dpoly} = 15 \text{ Å}$ , what is the effective increase in  $T_{or}$ ?

# Effect of Poly-Gate Depletion on $Q_{inv}$

$$Q_{inv} = C_{ox}(V_g - \phi_{poly} - V_t)$$

- Poly-gate depletion degrades

MOSFET current and circuit speed.

- How can poly-depletion be minimized?

### EXAMPLE : Poly-Silicon Gate Depletion

$V_{ox}$ , the voltage across a 2 nm thin oxide, is -1 V. The  $P^+$  polygate doping is  $N_{poly} = 8 \times 10^{19}$  cm<sup>-3</sup> and substrate  $N_d$  is  $10^{17}$ cm<sup>-3</sup>. Find (a)  $W_{dpoly}$ , (b)  $\phi_{poly}$ , and (c)  $V_g$ .

#### Solution:

(a)

$$W_{dpoly} = \varepsilon_{ox} \mathbf{E}_{ox} / qN_{poly} = \varepsilon_{ox} V_{ox} / T_{ox} qN_{poly}$$

$$= \frac{3.9 \times 8.85 \times 10^{-14} (\text{F/cm}) \times 1 \text{V}}{2 \times 10^{-7} \text{cm} \times 1.6 \times 10^{-19} \text{C} \times 8 \times 10^{19} \text{cm}^{-3}}$$

$$= 1.3 \text{ nm}$$

## EXAMPLE : Poly-Silicon Gate Depletion

$$(b) W_{dpoly} = \sqrt{\frac{2\varepsilon_s \phi_{poly}}{qN_{poly}}}$$

$$\phi_{dpoly} = qN_{poly}W_{dpoly}^2 / 2\varepsilon_s = 0.11 \,\mathrm{V}$$

$$(c) \quad V_g = V_{fb} + \phi_{st} + V_{ox} + \phi_{poly}$$

$$V_{fb} = \frac{E_g}{q} - \frac{kT}{q} \ln \left( \frac{N_c}{N_d} \right) = 1.1 \text{ V} - 0.15 \text{ V} = 0.95 \text{ V}$$

$$V_g = 0.95 \text{ V} - 0.85 \text{ V} - 1 \text{ V} - 0.11 \text{ V} = -1.01 \text{ V}$$

Is the loss of 0.11 V from the 1.01 V significant?

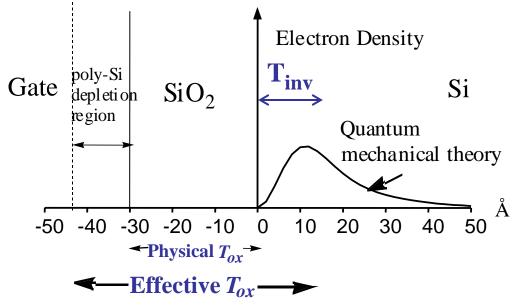

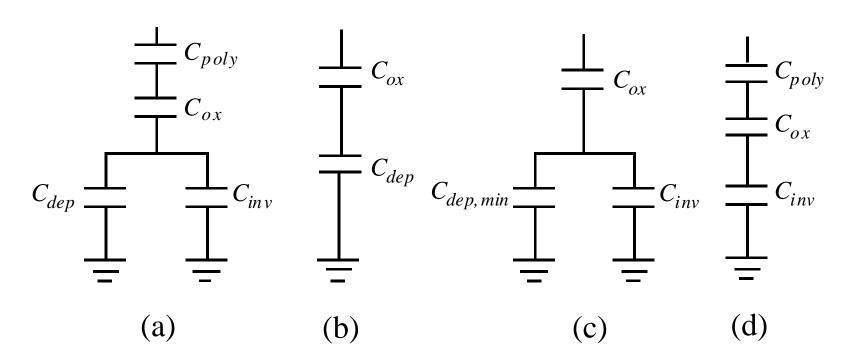

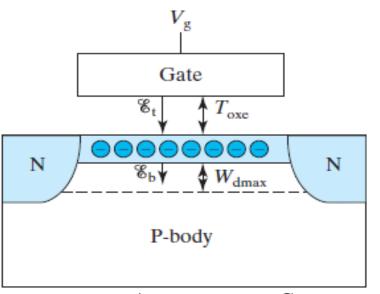

# 5.9 Inversion and Accumulation Charge-Layer Thickness—Quantum Mechanical Effect

Average inversion-layer location below the  $Si/SiO_2$  interface is called the *inversion-layer thickness*,  $T_{inv}$ .

n(x) is determined by Schrodinger's eq., Poisson eq., and Fermi function.

- $T_{inv}$  is a function of the average electric field in the inversion layer, which is  $(V_g + V_t)/6T_{ox}$  (Sec. 6.3.1).

- $T_{inv}$  of holes is larger than that of electrons because of difference in effective mass.

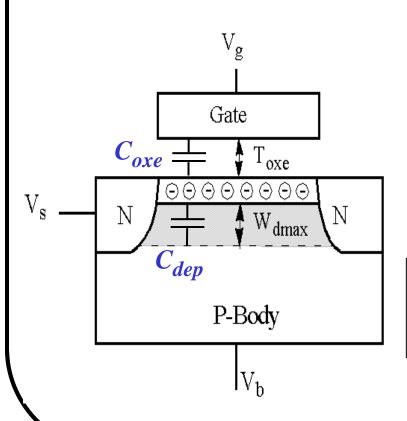

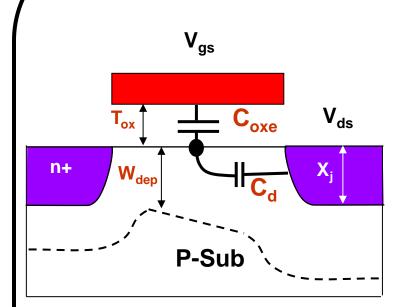

- • $T_{oxe}$  is the electrical oxide thickness.

$$T_{oxe} = T_{ox} + W_{dpoly} / 3 + T_{inv} / 3$$

at  $V_g = V_{dd}$

# Effective Oxide Thickness and Effective Oxide Capacitance

$$Q_{inv} = C_{oxe}(V_g - V_t)$$

$$T_{oxe} = T_{ox} + W_{dpoly} / 3 + T_{inv} / 3$$

#### Equivalent circuit in the depletion and the inversion regimes

General case for both depletion and inversion regions.

In the depletion regions

$V_{\rm g} \approx V_{\rm t}$

Strong inversion

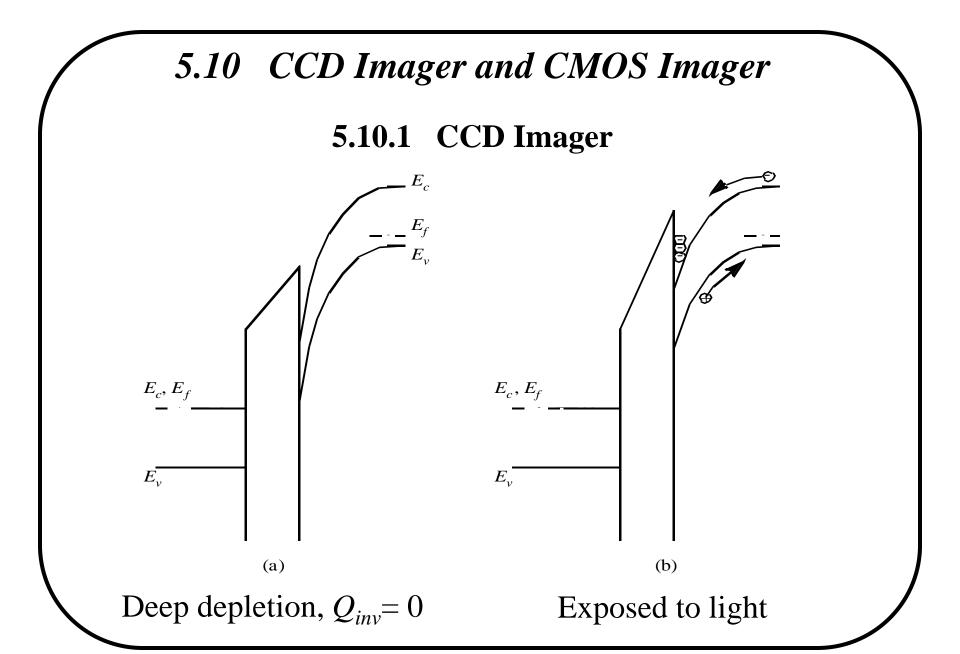

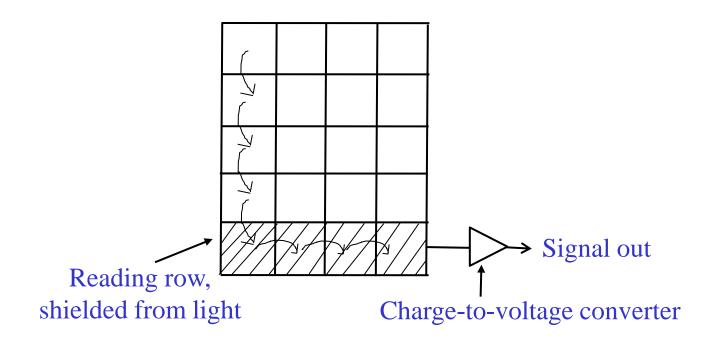

# two-dimensional CCD imager

The reading row is shielded from the light by a metal film. The 2-D charge packets are read row by row.

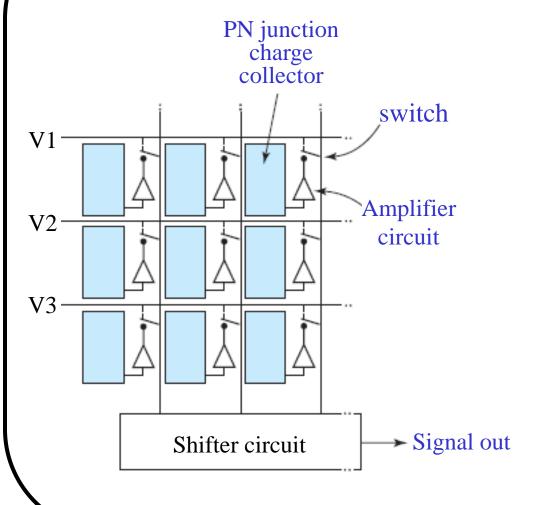

### 5.10.2 CMOS Imager

CMOS imagers can be integrated with signal processing and control circuitries to further reduce system costs. However, The size constrain of the sensing circuits forces the CMOS imager to use very simple circuits

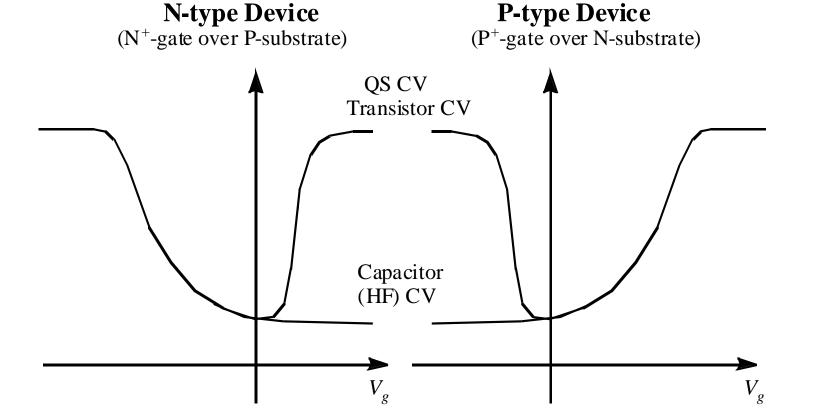

#### 5.11 Chapter Summary

N-type device: N<sup>+</sup>-polysilicon gate over P-body

P-type device: P<sup>+</sup>-polysilicon gate over N-body

$$V_{fb} = \psi_g - \psi_s + (-Q_{ox} / C_{ox})$$

$$V_g = V_{fb} + \phi_s + V_{ox} + \phi_{poly}$$

$$= V_{fb} + \phi_s - Q_s / C_{ox} + \phi_{poly}$$

#### 5.11 Chapter Summary

$$\phi_{st} = \pm 2\phi_B \text{ or } \pm (\phi_B + 0.45 \text{ V})$$

$$\phi_B = \frac{kT}{q} \ln \frac{N_{sub}}{n_i}$$

$$V_{t} = V_{fb} + \phi_{st} \pm \frac{\sqrt{qN_{sub} 2\varepsilon_{s} |\phi_{st}|}}{C_{ox}}$$

+ : N-type device, - : P-type device

## 5.11 Chapter Summary

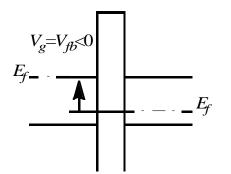

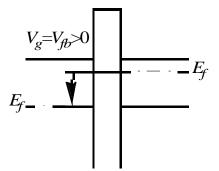

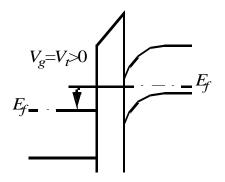

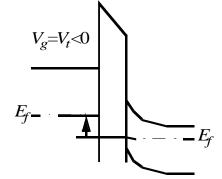

#### **N-type Device**

#### **P-type Device**

(N<sup>+</sup>-gate over P-substrate) (P<sup>+</sup>-gate over N-substrate)

Flat-band

Threshold

What's the diagram like at  $V_g > V_t$ ? at  $V_g = 0$ ?

What is the root cause of the low *C* in the HF CV branch?

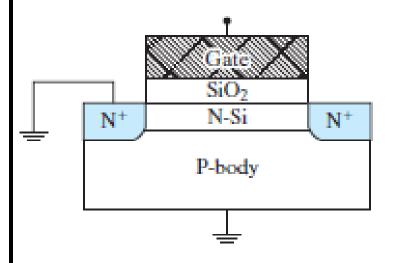

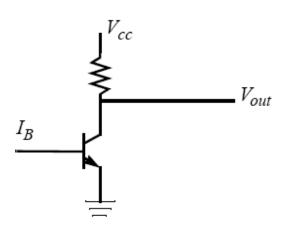

# Chapter 6 MOSFET

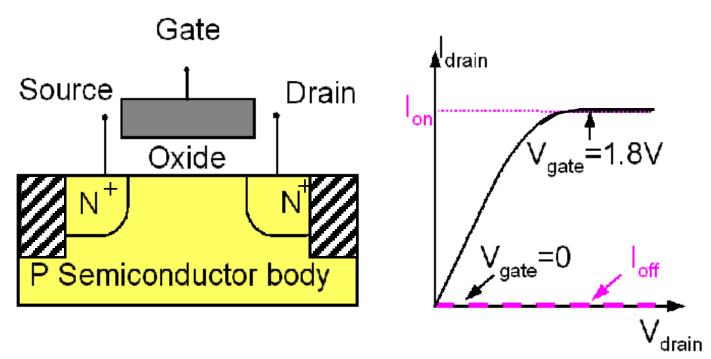

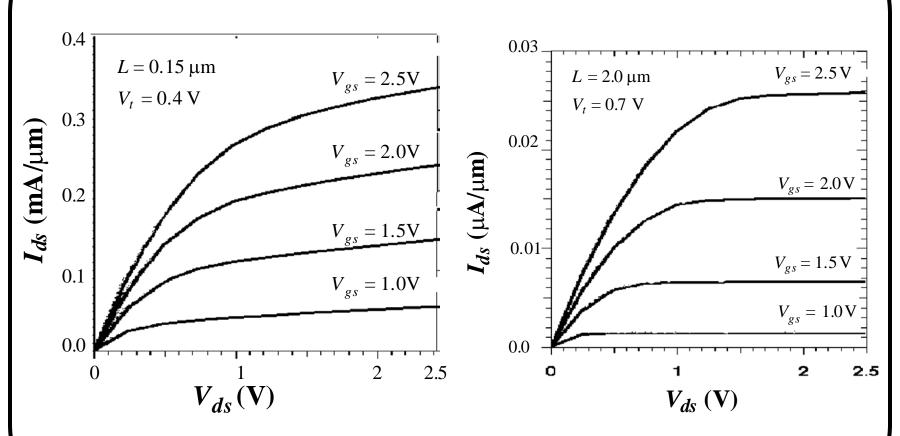

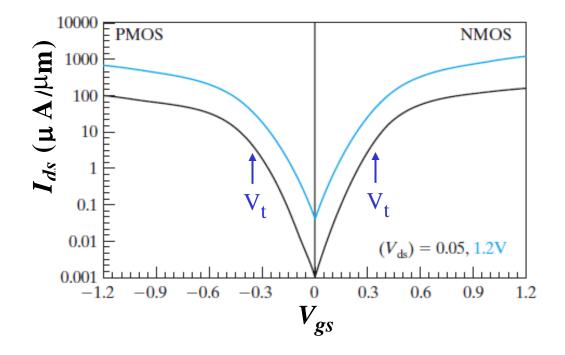

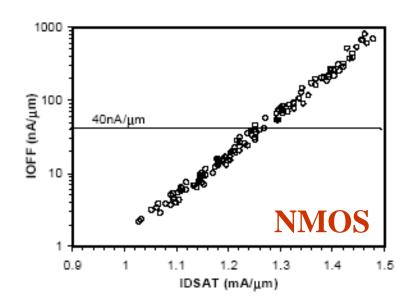

The MOSFET (MOS Field-Effect Transistor) is the building block of Gb memory chips, GHz microprocessors, analog, and RF circuits.

Match the following MOSFET characteristics with their applications:

- small size

- high speed

- low power

- high gain

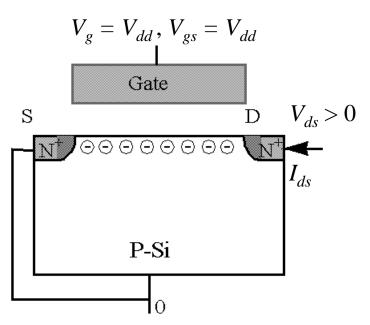

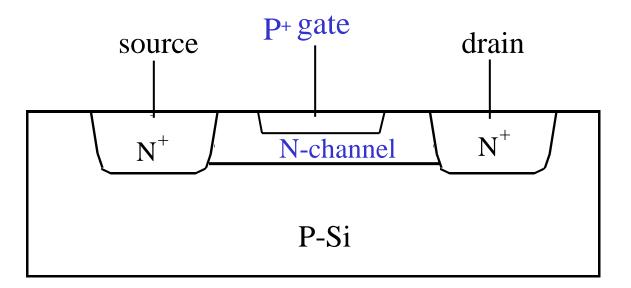

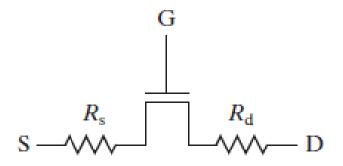

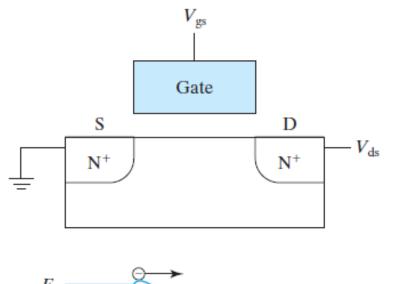

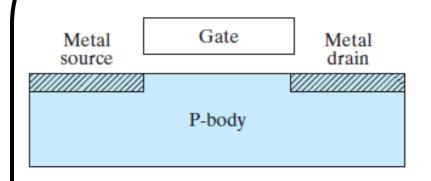

#### 6.1 Introduction to the MOSFET

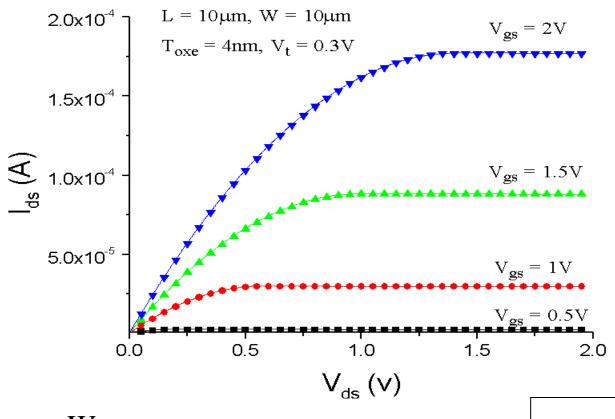

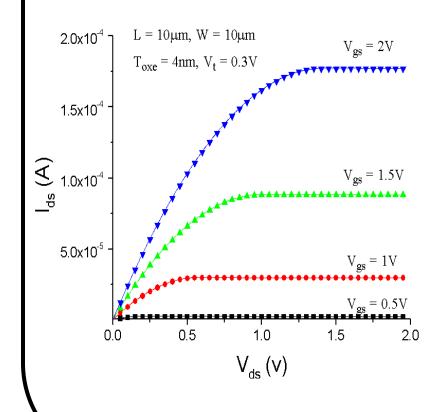

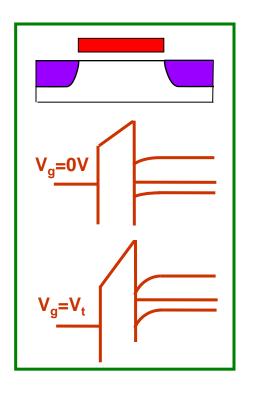

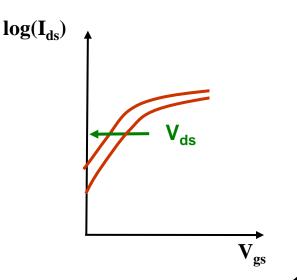

Basic MOSFET structure and IV characteristics

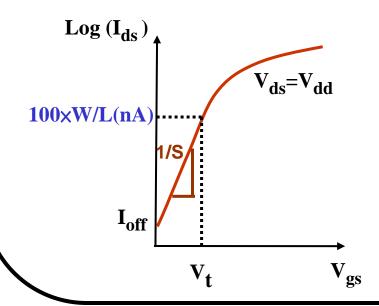

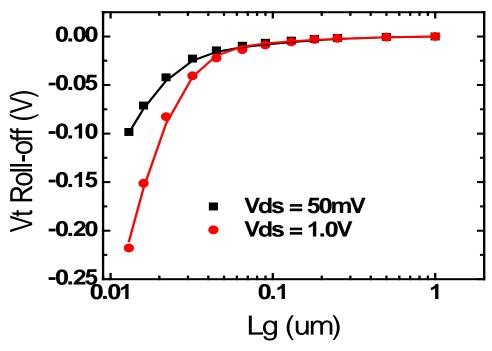

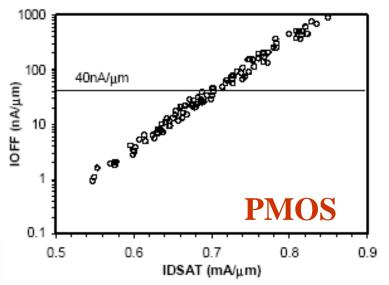

What is desirable: large I<sub>on</sub>, small I<sub>off</sub>

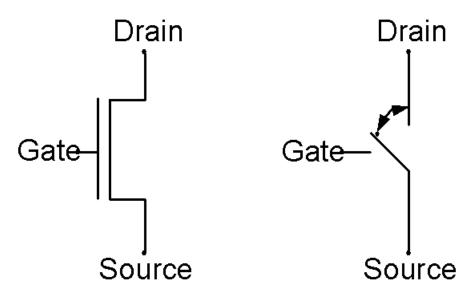

#### 6.1 Introduction to the MOSFET

Two ways of representing a MOSFET:

Circuit Symbol Simple Switch

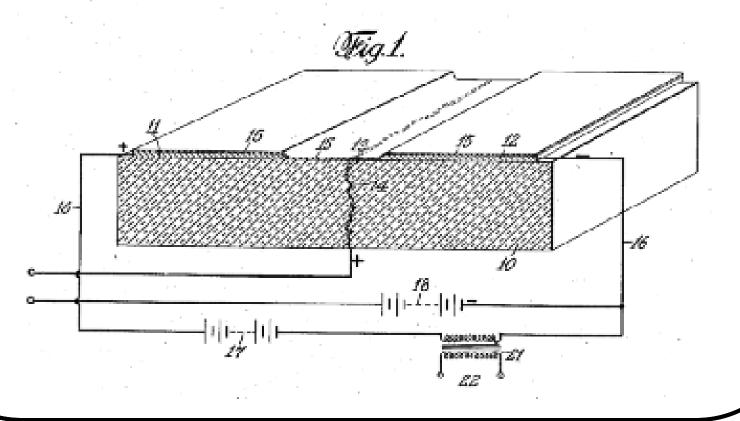

## Early Patents on the Field-Effect Transistor

Jan. 23, 1930.

J. E. LILIENFELD

1,745,175

METHOD AND APPARATUS FOR CONTROLLING ELECTRIC CURRENTS

Filed Oct. 8, 1926

#### Early Patents on the Field-Effect Transistor

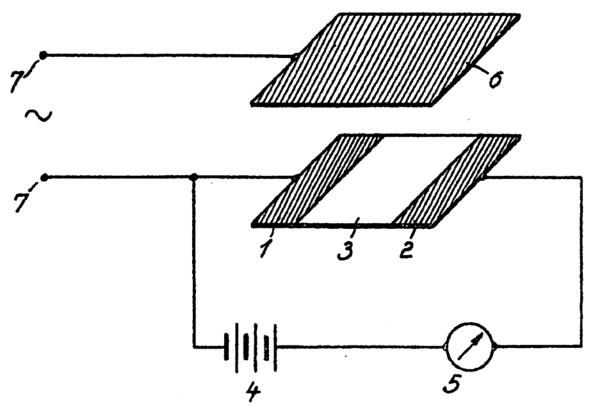

In 1935, a British patent was issued to Oskar Heil. A working MOSFET was not demonstrated until 1955. Using today's terminology, what are 1, 2, and 6?

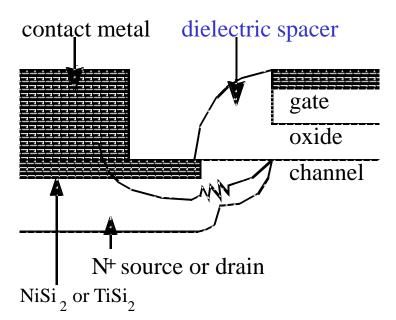

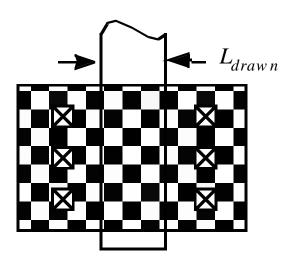

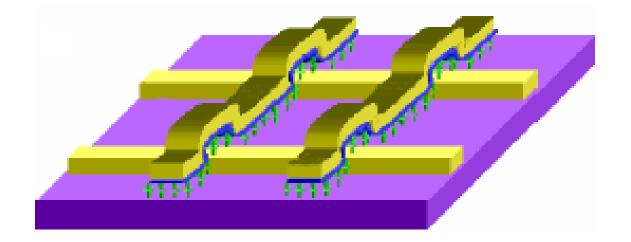

## 6.2 MOSFETs Technology

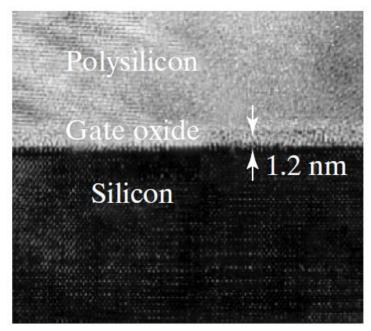

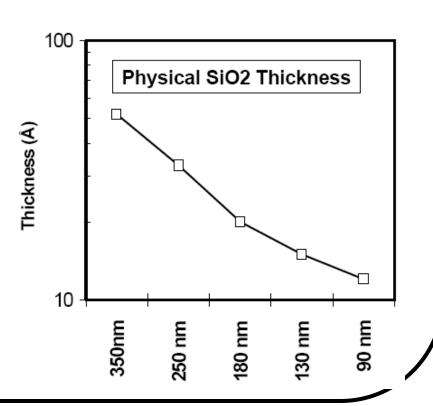

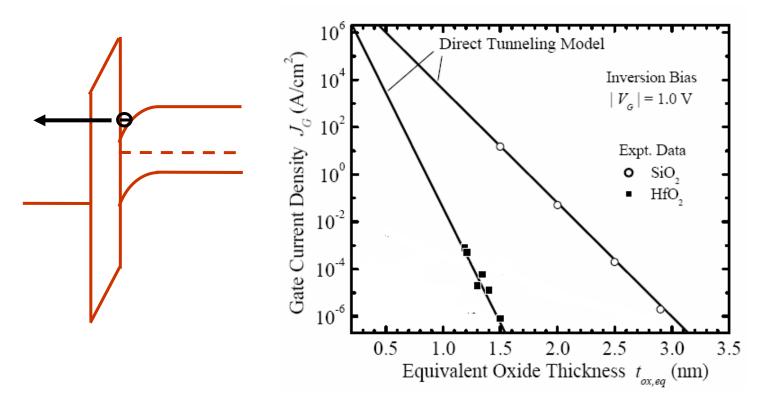

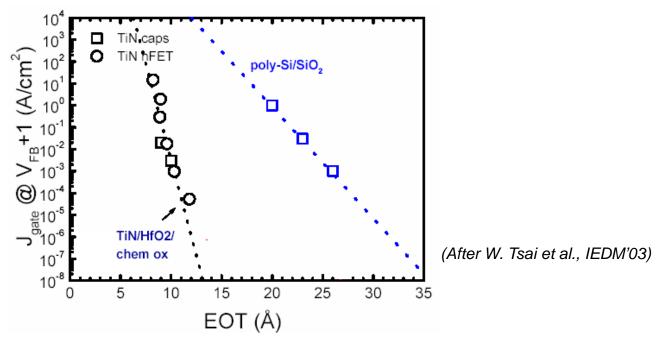

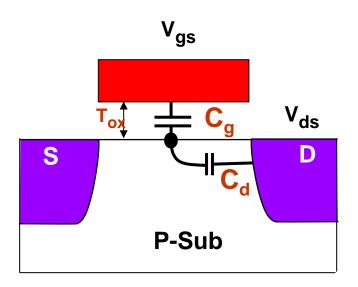

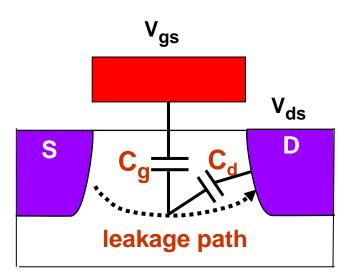

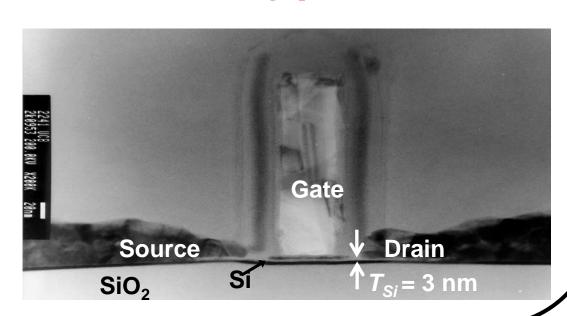

Polysilicon gate and 1.2nm SiO<sub>2</sub>

•1.2 nm SiO<sub>2</sub> used in production. Leakage current through the oxide limits further thickness reduction.

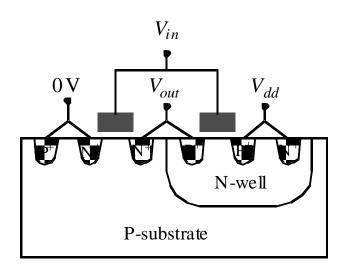

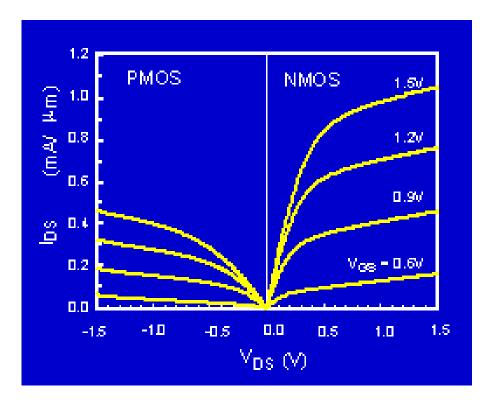

### 6.2 Complementary MOSFETs Technology

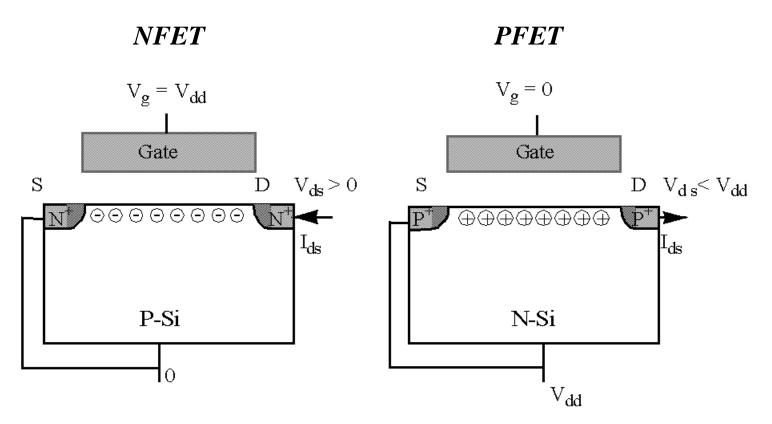

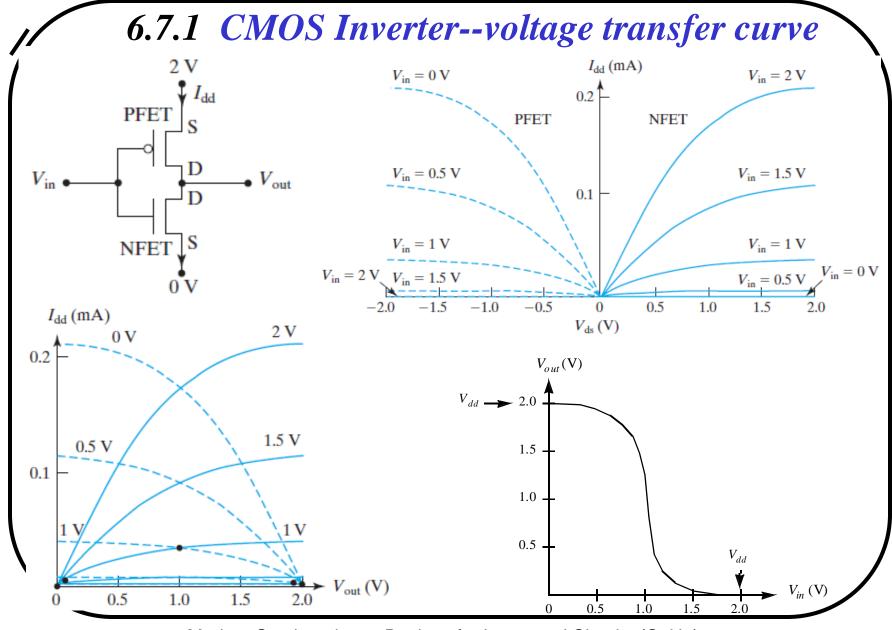

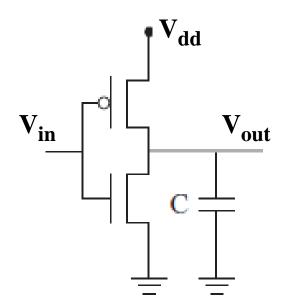

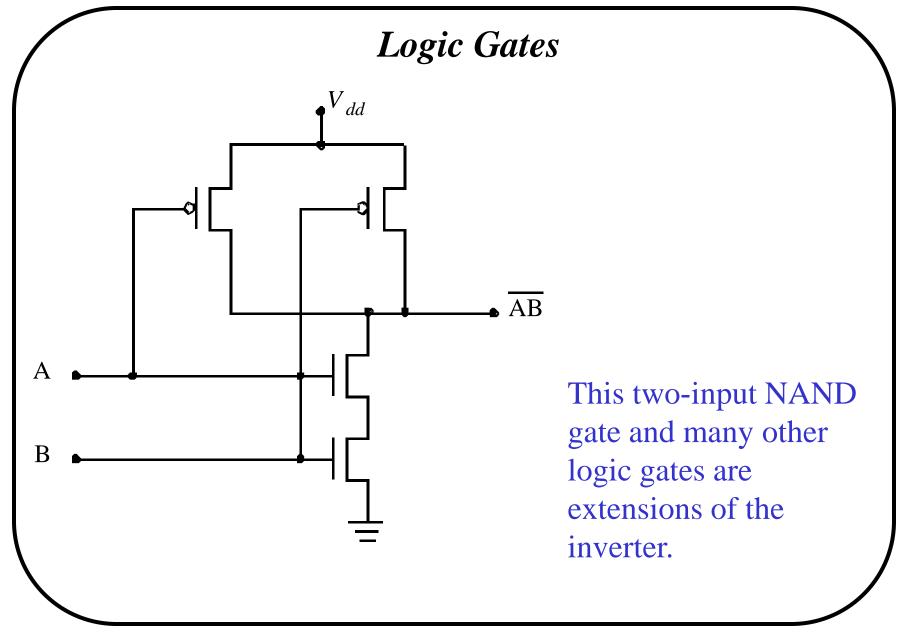

When  $V_g = V_{dd}$ , the NFET is on and the PFET is off. When  $V_g = 0$ , the PFET is on and the NFET is off.

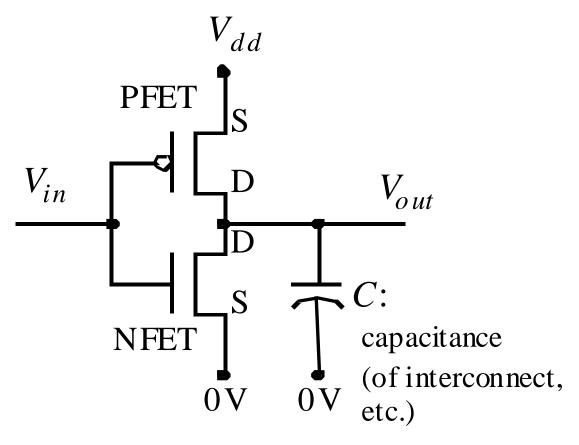

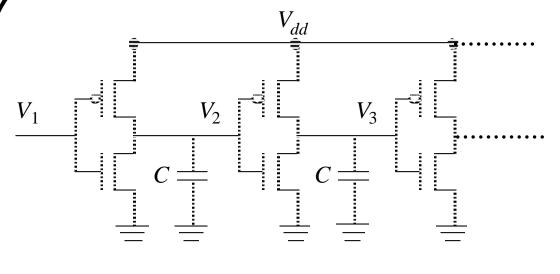

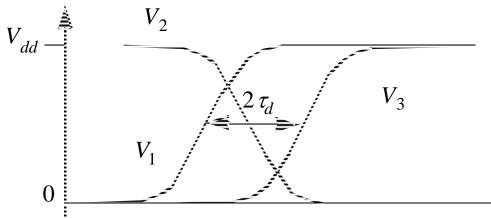

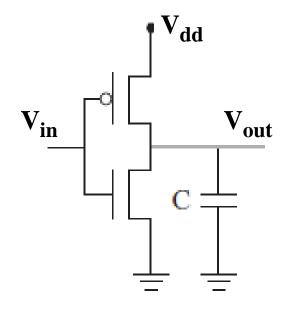

### CMOS (Complementary MOS) Inverter

A CMOS inverter is made of a PFET *pull-up device* and a NFET *pull-down device*.  $V_{out} = ?$  if  $V_{in} = 0$  V.

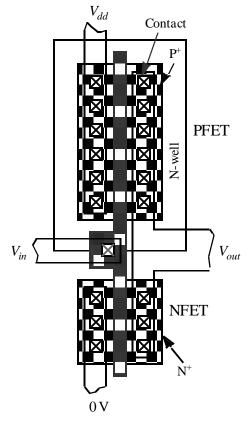

#### CMOS (Complementary MOS) Inverter

• NFET and PFET can be fabricated on the same chip.

basic layout of a CMOS inverter

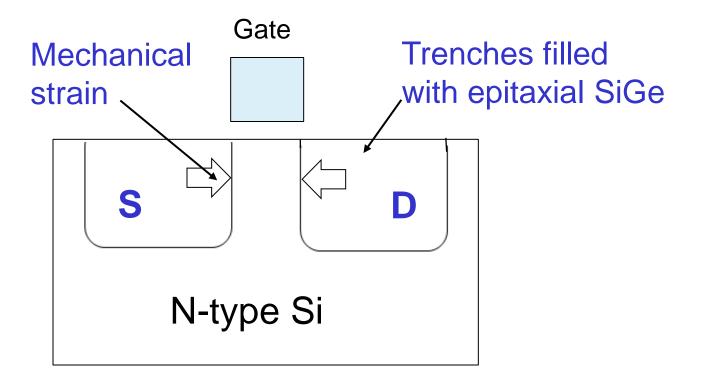

## 6.3 Surface Mobilities and High-Mobility FETs

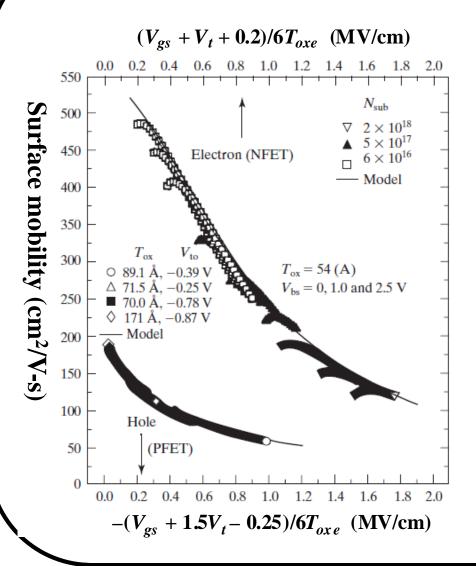

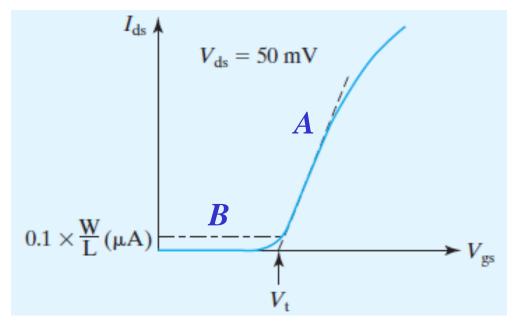

### 6.3.1 Surface Mobilities

How to measure the surface mobility:

$$I_{ds} = W \times Q_{inv} \times v = WQ_{inv} \mu_{ns} \mathbf{E} = WQ_{inv} \mu_{ns} V_{ds} / L$$

$$= WC_{oxe} (V_{gs} - V_t) \mu_{ns} V_{ds} / L$$

# Mobility is a function of the average of the fields at the bottom and the top of the inversion charge layer, $\mathbf{E}_b$ and $\mathbf{E}_t$ .

From Gauss's Law,

$$\mathbf{E}_b = -Q_{dep}/\mathcal{E}_s$$

$$V_{t} = V_{fb} + \phi_{st} - Q_{dep} / C_{oxe}$$

Therefore,

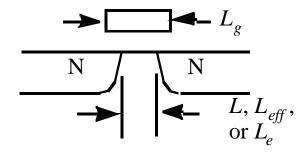

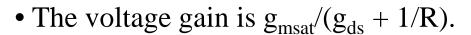

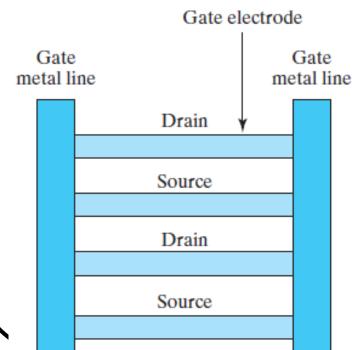

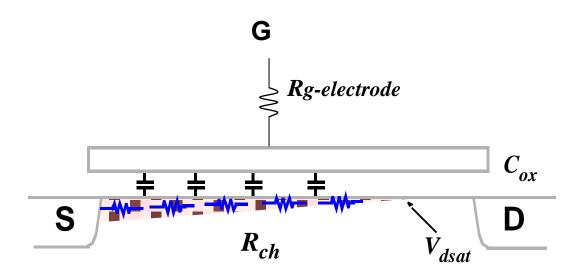

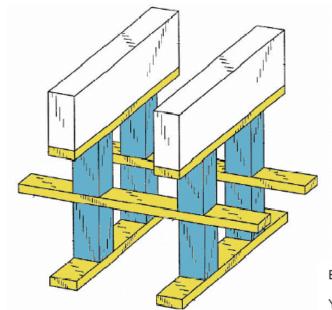

$$\mathbf{E}_{b} = \frac{C_{oxe}}{\mathcal{E}_{s}} (V_{t} - V_{fb} - \phi_{st})$$